GigE Vision® Device Package

High-speed image data transfer compliant with GigE Vision standard

The GigE Vision Device Package is an interface IP package for the transfer of image data complying with industrial GigE Vision camera standards. The IP transmits image data from the image sensor to Gigabit Ethernet in real-time. Users can build highly reliable products using its high-speed transfer capability and high-precision time synchronization.

The GigE Vision Device Package is an interface IP package for the transfer of image data complying with industrial GigE Vision camera standards. The IP transmits image data from the image sensor to Gigabit Ethernet in real-time. Users can build highly reliable products using its high-speed transfer capability and high-precision time synchronization.

GigE Vision is optimized for high-resolution, high-reliable machine vision cameras, medical imaging systems, and other applications that demand maximized Gigabit Ethernet performance. In addition to 1Gbps compatible GigE Vision IP, nBase-T compatible IP up to 10Gbps is also a

Features

- Highly reliable, high-precision image transmission using the GigE Vision and 10GigE Vision protocols

- 995 Mbps or 9.5 Gbps maximum effective transfer rate

- Comprehensive reference environment

- GigE Vision Compliant, certified by the Automated Imaging Association (AIA)

- Interoperability qualified with various GenICam application vendors

- Supports IEEE1588 PTP (Precision Time Protocol) as Master and Slave

Specifications

- Compliant with GigE Vision Standard Version 1.2/Version 2.0

- Supports IEEE1588-2008 PTP

- Compliant with EMVA GenICam Standard Version 3.0.1

- Supports Packet Re-transmission

- Other functions

- Chunk data transfer, GigE Vision action commands, Timestamp, Packet delay

- Image data (RGB, YUV, etc.) and RAW data transfer

Supported Devices

- 1GigE: Intel Cyclone V

- 10GigE: Intel Cyclone 10 GX

* Please contact Macnica sales department about other devices.

Deliverable

- Encrypted RTL (Verilog HDL)

- GigE Vision Device FW Library for Nios II processors

- Reference environment (sample hardware design, firmware application, Windows PC software)

- User’s manual

* Please contact Macnica sales department for information about other deliverables.

Device Resource Utilization

- Cyclone V

- Logic utilization (in ALMs) : 20,749.5

- Total registers: 37,430

- Total block memory (M20Ks): 233

- DSP Blocks: 14

- Cyclone 10 GX

- Logic utilization (in ALMs) : 15,085.5

- Total registers: 37, 467

- Total block memory (M20Ks): 56

- DSP Blocks: 9

* The values in the above table are based on an implementation example. There may be some variation depending on the user’s system configuration.

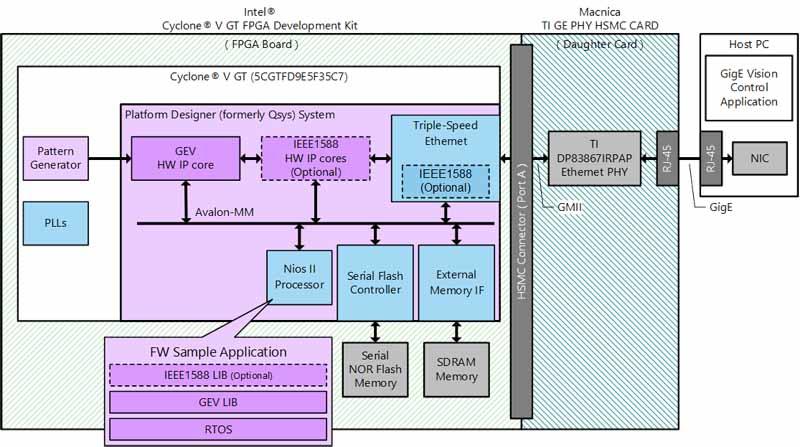

Reference Block Diagram

* Dark purple areas indicate the IP.

Evaluation Environment