Altera Agilex 5 devices serve a broad range of applications that require high performance, lower power, and smaller form factors. This tier consists of the performance-optimized D-Series FPGAs and the power-optimized E-Series FPGAs. Altera Agilex 5 devices also feature the industry’s first Enhanced DSP with AI Tensor Block, which deliver high-efficiency AI and digital signal processing (DSP) functionality, and the FPGA industry’s first asymmetric applications processor system consisting of dual Arm Cortex-A76 cores and dual Cortex-A55 cores, which enable you to optimize the performance and power efficiency of their workloads. These characteristics make them ideal for midrange FPGA applications across the edge and core including wireless and wireline communications, video and broadcast equipment, industrial applications, test and measurement products, medical electronics, and defense applications.

E-Series FPGAs and SoCs |

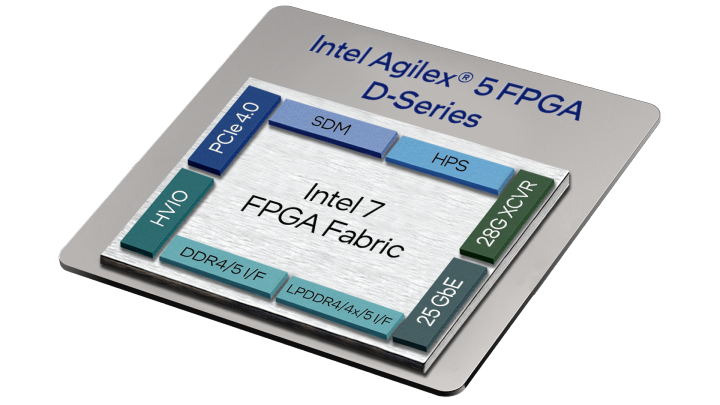

D-Series FPGAs and SoCs |

|

|

| E-Series FPGAs and SoCs are optimized for power and size— with 50% lower power while delivering up to 2.5X better performance as compared to Cyclone V devices, also with features including transceiver rates up to 24x28 Gbps, PCIe 4.0x4, 6x25GbE, 3,600 Mbps DDR5, dual core of A55 and dual core of A76 make it ideal for intelligent applications at the edge, embedded, and more. | D-Series FPGAs and SoCs are optimized for performance and power efficiency— with 42% lower power while delivering up to 1.5X better performance as compared to Intel Stratix 10 FPGAs, also with features including transceiver rates up to 32x28 Gbps, PCIe 4.0x8, 16x25GbE, 4,000 Mbps DDR5, dual core of A55 and dual core of A76 make it deal for various applications across multiple markets |

Altera Agilex® 5 FPGAs and SoCs E-Series Product Table - Device Group A

PRODUCT LINE |

A5E 013A |

A5E 028A |

A5E 043A |

A5E 052A |

A5E 065A |

||||

| Resources | Logic elements (LEs) | 138,060 | 282,256 | 434,240 | 523,920 | 656,080 | |||

| Adaptive logic modules (ALMs) | 46,800 | 95,680 | 147,200 | 177,600 | 222,400 | ||||

| ALM registers | 68,400 | 93,600 | 588,800 | 710,400 | 889,600 | ||||

| M20K memory blocks | 358 | 716 | 1,050 | 1,288 | 1,611 | ||||

| M20K memory size (Mb) | 6.99 | 13.98 | 20.51 | 25.16 | 31.46 | ||||

| MLAB memory count | 2,340 | 4,784 | 6,720 | 8,440 | 11,120 | ||||

| MLAB memory size (Mb) | 1.0 | 1.8 | 2.4 | 2.8 | 4.3 | ||||

| I/O PLL | 4 | 4 | 8 | 8 | 8 | ||||

| Variable-precision digital signal processing (DSP) blocks | 188 | 376 | 564 | 676 | 846 | ||||

| 18 x 19 multipliers | 376 | 752 | 1,128 | 1,352 | 130 | ||||

| Peak INT8 (TOPS) | 5.78 | 11.55 | 17.33 | 20.78 | 25.99 | ||||

| Maximum Available Device Resources | LVDS pairs at 1.6 Gbps | 96 | 96 | 192 | 192 | 192 | |||

| DDR4/5 and LPDDR4/5 interfaces (x32) | 2 | 2 | 4 | 4 | 4 | ||||

| MIPI D-PHY interface | 14 | 14 | 28 | 28 | 28 | ||||

| Differential (RX or TX) pairs at 28 Gbps | 4 | 12 | 16 | 24 | 24 | ||||

| PCIe 4.0 x4 instance | 1 | 3 | 4 | 6 | 6 | ||||

| High-speed I/O (HSIO) | 192 | 192 | 384 | 384 | 384 | ||||

| High-voltage I/O (HVIO) | 200 | 200 | 120 | 120 | 120 | ||||

| Secure device manager (SDM) | Provides SHA-384 bitstream integrity, ECDSA 256/384 bitstream authentication, AES-256 bitstream encryption, physically unclonable function (PUF) protected key storage, side-channel attack resistance, SPDM attestation, cryptographic services, physical anti-tamper support | ||||||||

| Hard processor system | Multi-core with 32-bit/64-bit dual-core Arm Cortex-A55 up to 1.5 GHz with 32 KB I/D cache and 128 KB L2 cache, and dual-core Arm Cortex-A76 up to 1.8 GHz with 64 KB I/D cache and 256 KB L2 cache, and up to 2 MB L3 shared cache, multi-channels direct memory access (DMA), 512 KB on-chip RAM, USB 3.1 x1, USB 2.0 OTG x2, TSN MAC x3, UART x2, SPI M x2, SPI S x2, I3C x2, I2C x5, NAND x1, SDMMC x1, Osc timer x2, SP timer x2, watchdog x5, GPIO x2. | ||||||||

| Transceiver | PCI Express (PCIe) hard IP up to PCIe 4.0 x4 EP and RP Transceiver channel count: up to 24 channels at 28 Gbps (NRZ) Ethernet IP: up to 6 x10/25 GbE hard IP (MAC, PCS, and FEC) | ||||||||

| Package Options3 and I/O Pins4: General-Purpose I/O (GPIO) Count, High-Voltage I/O Count, LVDS Pairs5, and Transceiver Count | |||||||||

| B23A | 120/96/4 | 120/96/12 | 120/96/12 | 120/96/12 | 120/96/12 | ||||

| B32A | 200/192/4 | 200/192/12 | 120/384/16 | 120/384/24 | 120/384/24 | ||||

Altera Agilex® 5 FPGAs and SoCs E-Series Product Table - Device Group B

PRODUCT LINE |

A5E 005B |

A5E 007B |

A5E 008B |

A5E 013B |

A5E 028B |

A5E 043B | A5E052BA | A5E065B | ||||

| Resources | Logic elements (LEs) | 50,445 | 69,030 | 85,196 | 138,060 | 282,256 | 434,240 | 523,920 | 656,080 | |||

| Adaptive logic modules (ALMs) | 17,100 | 23,400 | 28,880 | 46,800 | 95,680 | 147,200 | 177,600 | 222,400 | ||||

| ALM registers | 68,400 | 93,600 | 115,520 | 187,200 | 382,720 | 588,800 | 710,400 | 889,600 | ||||

| M20K memory blocks | 130 | 179 | 229 | 358 | 716 | 1,050 | 1,288 | 1,611 | ||||

| M20K memory size (Mb) | 2.54 | 3.50 | 4.47 | 6.99 | 13.98 | 20.51 | 25.16 | 31.46 | ||||

| MLAB memory count | 850 | 1,170 | 1,780 | 2,340 | 4,784 | 6,720 | 8,440 | 11,120 | ||||

| MLAB memory size (Mb) | 0.52 | 0.71 | 1.09 | 1.43 | 2.92 | 4.10 | 5.13 | 6.79 | ||||

| I/O PLL | 2 | 2 | 4 | 4 | 4 | 8 | 8 | 8 | ||||

| Variable-precision digital signal processing (DSP) blocks | 65 | 94 | 116 | 188 | 376 | 564 | 676 | 846 | ||||

| 18 x 19 multipliers | 130 | 188 | 232 | 376 | 752 | 1,128 | 1,352 | 1,692 | ||||

| Peak INT8 (TOPS) | 1.7 | 2.46 | 3.05 | 4.93 | 9.85 | 14.78 | 17.72 | 22.17 | ||||

| Maximum Available Device Resources | LVDS pairs at 1.6 Gbps | 48 | 48 | 96 | 96 | 96 | 192 | 192 | 192 | |||

| DDR4/5 and LPDDR4/5 interfaces (x32) | 1 | 1 | 2 | 2 | 2 | 4 | 4 | 4 | ||||

| MIPI D-PHY interface | 7 | 7 | 14 | 14 | 14 | 28 | 28 | 28 | ||||

| Differential (RX or TX) pairs at 28 Gbps | 0 | 0 | 4 | 4 | 12 | 16 | 24 | 24 | ||||

| PCIe 4.0 x4 instance | 0 | 0 | 1 | 1 | 3 | 4 | 6 | 6 | ||||

| High-speed I/O (HSIO) | 96 | 96 | 192 | 192 | 192 | 384 | 384 | 384 | ||||

| High-voltage I/O (HVIO) | 160 | 160 | 200 | 200 | 200 | 120 | 120 | 120 | ||||

| Secure device manager (SDM) | Provides SHA-384 bitstream integrity, ECDSA 256/384 bitstream authentication, AES-256 bitstream encryption, physically unclonable function (PUF) protected key storage, side-channel attack resistance, SPDM attestation, cryptographic services, physical anti-tamper support | |||||||||||

| Hard processor system | Multi-core with 32-bit/64-bit dual-core Arm Cortex-A55 up to 1.5 GHz with 32 KB I/D cache and 128 KB L2 cache, and dual-core Arm Cortex-A76 up to 1.8 GHz with 64 KB I/D cache and 256 KB L2 cache, and up to 2 MB L3 shared cache, multi-channels direct memory access (DMA), 512 KB on-chip RAM, USB 3.1 x1, USB 2.0 OTG x2, TSN MAC x3, UART x2, SPI M x2, SPI S x2, I3C x2, I2C x5, NAND x1, SDMMC x1, Osc timer x2, SP timer x2, watchdog x5, GPIO x2. | |||||||||||

| Transceiver | PCI Express (PCIe) hard IP up to PCIe 4.0 x4 EP and RP Transceiver channel count: up to 24 channels at 28 Gbps (NRZ) Ethernet IP: up to 6 x10/25 GbE hard IP (MAC, PCS, and FEC) | |||||||||||

| Package Options3 and I/O Pins4: General-Purpose I/O (GPIO) Count, High-Voltage I/O Count, LVDS Pairs5, and Transceiver Count | ||||||||||||

| B15A | 80/62 | 80/62 | ||||||||||

| M16A | 40/192/4 | 40/192/4 | 40/192/8 | |||||||||

| B18A | 160/52 | 160/52 | ||||||||||

| B23B | 160/96 | 160/96 | 160/192 | 160/192 | 160/192 | |||||||

| B23A | 120/96/4 | 120/96/4 | 120/96/12 | 120/96/12 | 120/96/12 | 120/96/12 | ||||||

| B32A( | 200/192/4 | 200/192/4 | 200/192/12 | 120/384/16 | 120/384/ | 120/384/24 | ||||||

Altera Agilex® 5 FPGAs and SoCs D-Series Product Table

PRODUCT LINE |

A5D 010 |

A5D 025 |

A5D 031 |

A5D 051 |

A5D 064 |

||||

| Resources | Logic elements (LEs) | 103,250 | 254,054 | 318,600 | 515,070 | 644,280 | |||

| Adaptive logic modules (ALMs) | 35,000 | 86,120 | 108,000 | 174,600 | 218,400 | ||||

| ALM registers | 140,000 | 344,480 | 432,000 | 698,400 | 873,600 | ||||

| M20K memory blocks | 534 | 1,281 | 1,602 | 2,563 | 3,204 | ||||

| M20K memory size (Mb) | 10.43 | 25.02 | 31.29 | 50.06 | 62.58 | ||||

| MLAB memory count | 1780 | 3420 | 5,400 | 8,440 | 10,920 | ||||

| MLAB memory size (Mb) | 1.09 | 2.09 | 3.30 | 5.15 | 6.67 | ||||

| I/O PLL | 8 | 8 | 8 | 8 | 8 | ||||

| Variable-precision digital signal processing (DSP) blocks | 276 | 736 | 920 | 1,472 | 1,840 | ||||

| 18 x 19 multipliers | 552 | 1,472 | 1,840 | 2,944 | 3,680 | ||||

| Peak INT8 (TOPS) | 8.48 | 22.61 | 28.26 | 45.22 | 56.22 | ||||

| Maximum Available Device Resources | LVDS pairs at 1.6 Gbps | 192 | 192 | 192 | 192 | 192 | |||

| DDR4/5 and LPDDR4/5 interfaces (x32) | 2 | 2 | 2 | 2 | 2 | ||||

| MIPI D-PHY interface | 28 | 28 | 28 | 28 | 28 | ||||

| Differential (RX or TX) pairs at 28 Gbps | 16 | 16 | 16 | 24 | 32 | ||||

| PCIe 4.0 x4 instance | 4 | 4 | 4 | 6 | 8 | ||||

| High-speed I/O (HSIO) | 384 | 384 | 384 | 384 | 384 | ||||

| High-voltage I/O (HVIO) | 60 | 60 | 60 | 60 | 60 | ||||

| Secure device manager (SDM) | Provides SHA-384 bitstream integrity, ECDSA 256/384 bitstream authentication, AES-256 bitstream encryption, physically unclonable function (PUF) protected key storage, side-channel attack resistance, SPDM attestation, cryptographic services, physical anti-tamper support | ||||||||

| Hard processor system | Multi-core with 32-bit/64-bit dual-core Arm Cortex-A55 up to 1.5 GHz with 32 KB I/D cache and 128 KB L2 cache, and dual-core Arm Cortex-A76 up to 1.8 GHz with 64 KB I/D cache and 256 KB L2 cache, and up to 2 MB L3 shared cache, multi-channels direct memory access (DMA), 512 KB on-chip RAM, USB 3.1 x1, USB 2.0 OTG x2, TSN MAC x3, UART x2, SPI M x2, SPI S x2, I3C x2, I2C x5, NAND x1, SDMMC x1, Osc timer x2, SP timer x2, watchdog x5, GPIO x2. | ||||||||

| Transceiver | PCI Express (PCIe) hard IP up to PCIe 4.0 x4 EP and RP Transceiver channel count: up to 24 channels at 28 Gbps (NRZ) Ethernet IP: up to 6 x10/25 GbE hard IP (MAC, PCS, and FEC) | ||||||||

| Package Options3 and I/O Pins4: General-Purpose I/O (GPIO) Count, High-Voltage I/O Count, LVDS Pairs5, and Transceiver Count | |||||||||

| B23A | 60/192/8 | 60/192/8 | 60/192/8 | ||||||

| B32A | 60/384/16 | 60/384/16 | 60/384/16 | 60/384/24 | 60/384/32 | ||||

Altera Agilex® 5 FPGA Focus Markets

Image Sensor Processing

Inline image processing

- Pixel defect correction

- Vignette correction

- Adaptive noise reduction

Customized Connectivity

- High-definition multimedia interface (HDMI)

- MIPI D-PHY

Hard Processor System

- Flexible embedded software stack

- Graphical user interface

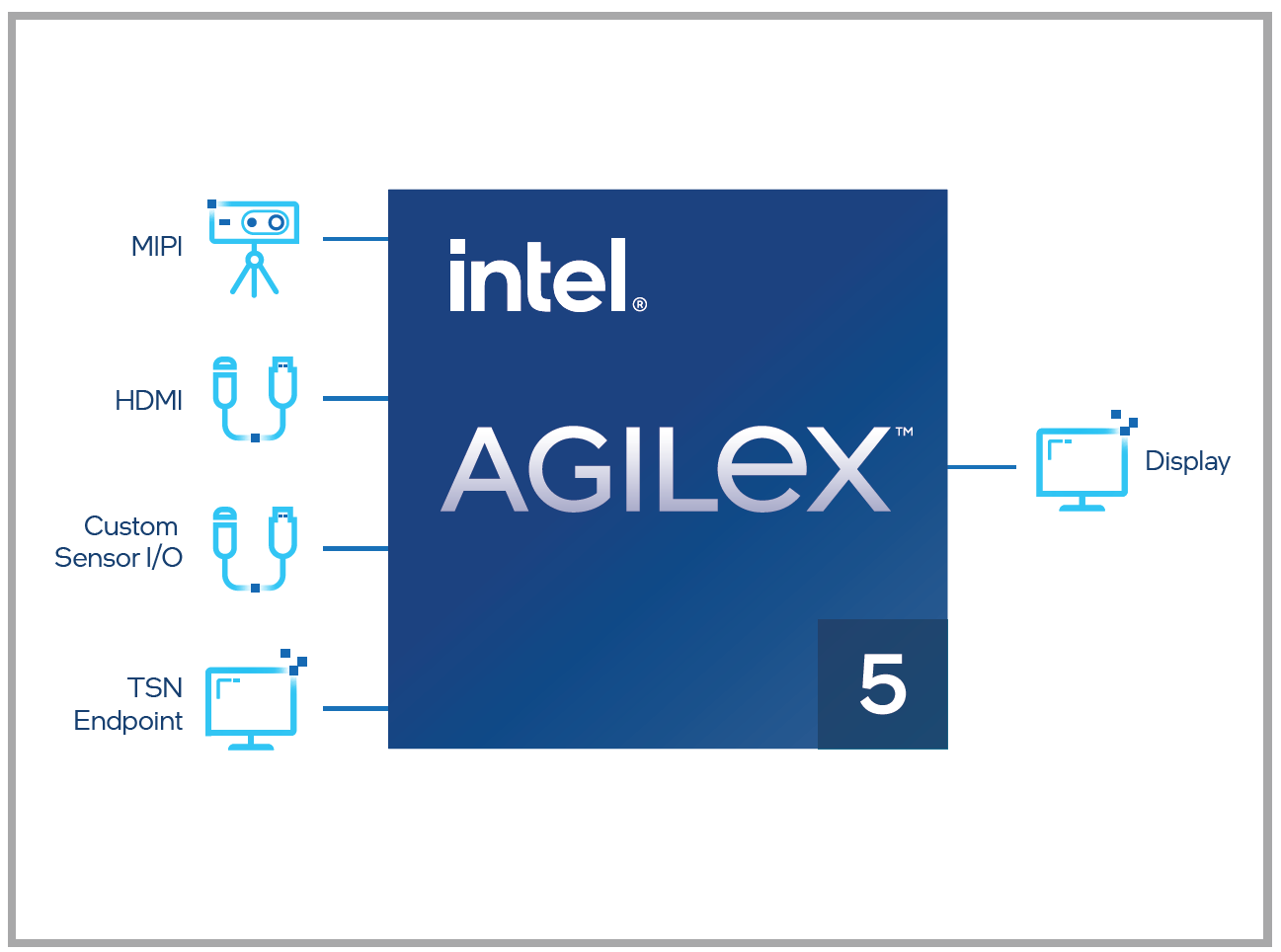

Autonomous Mobile Robots

Flexible I/O

- MIPI

- HDMI

- Time-Sensitive Networking (TSN)

- LVDS

FPGA Acceleration

- Sensor fusion

- Point of cloud processing

Hard Processor System

- RTOS

- Hypervisor functions

- Network features

- User application

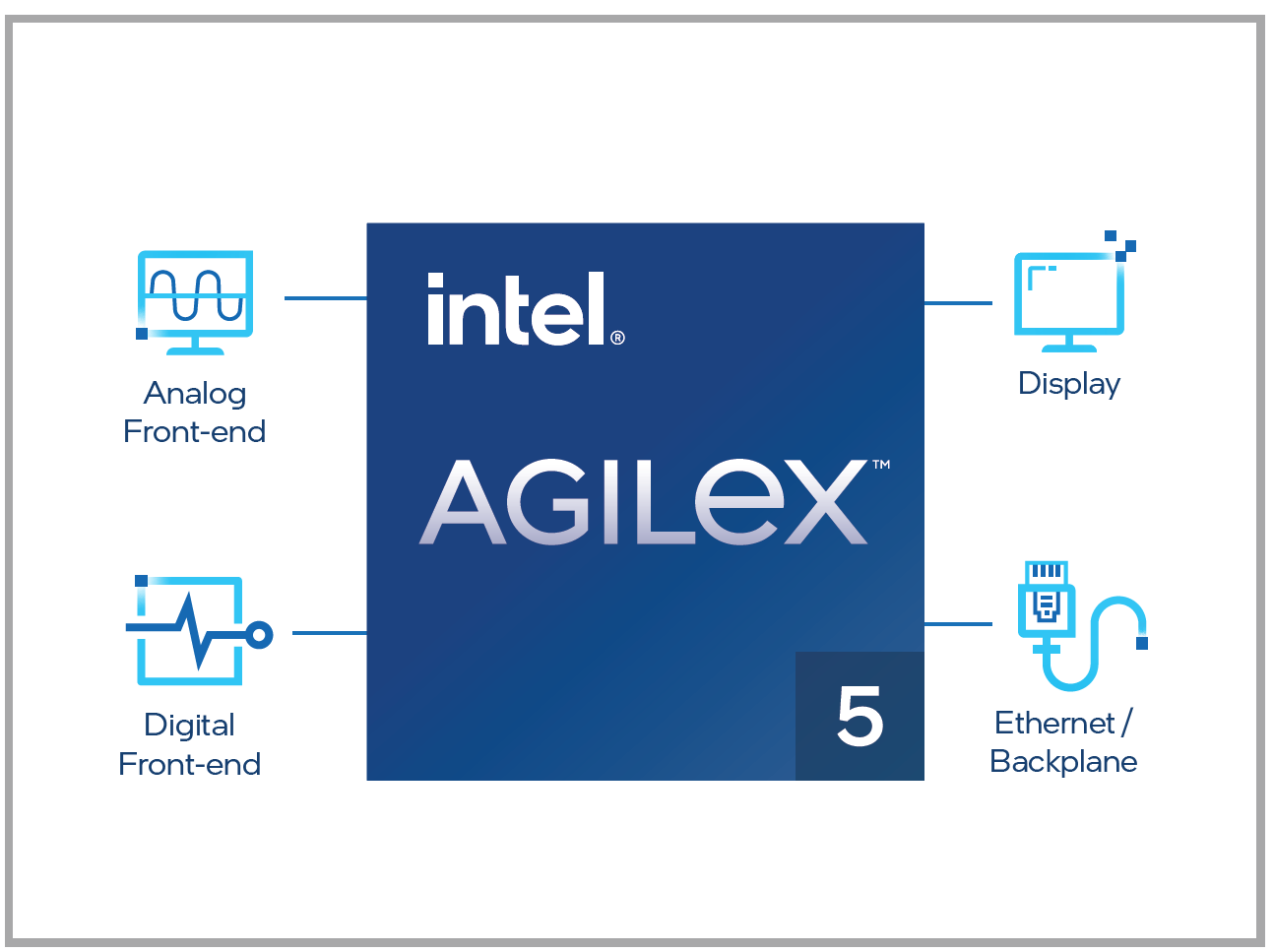

Clinical System

Power Optimized

- Low-density option

- Battery-powered clinical equipment

FPGA Acceleration

- Custom image progressing

- AR/VR innovations

- Deterministic low latency

Hard Processor System

- Real-time waveform analysis

- Graphic controls for Human-Machine Interaction (HMI)