Method of Reducing Communication Errors in the I2c Bus

When connecting multiple devices for memory and power sequence management on an FPGA board, you may be using the I2C bus. Some systems use the I2C bus between boards.

I2C bus is simple with 2 wires

The I2C bus only requires 2 line wires of single clock (SCL) and single data (SDA) to communicate between devices.

Because of its simplicity, it is increasingly being used by SMBus, PMBus, and ATCA's IPMB bus, which are used by communication devices.

It is simple but be careful of trouble

People tend to think that “The I2C bus is simple and easy to design because it is a 2 wire type with low speed communication”.

However, it is not rare to fall into a situation where communication is not good.

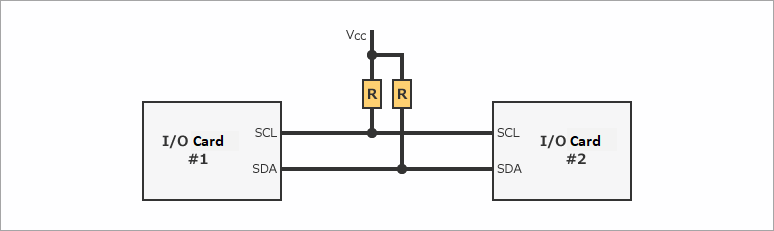

In particular, if a communication device needs to be connected to the backplane, or if the IO cards are connected to each other via long wires, the possibility of trouble is high.

What caused the communication error?

The most likely cause of the communication error is that the wiring capacity deviates from the requirements of the I2C bus. The I2C bus standard specifies a maximum wiring capacity of 400pF.

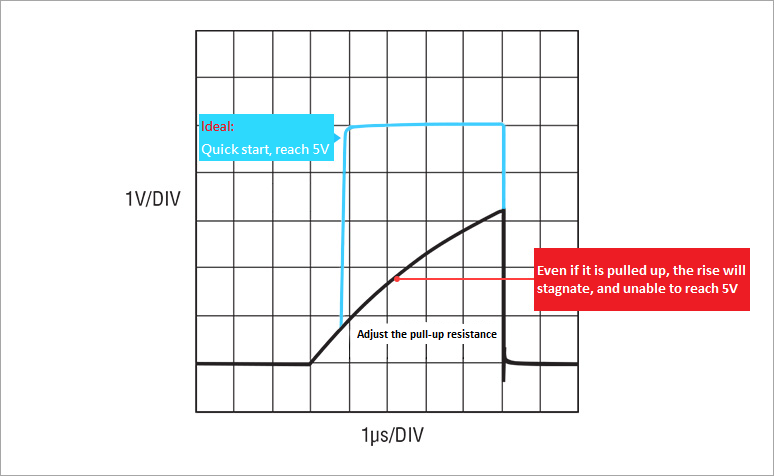

In the case of connecting to the backplane and long wiring between IO cards, the wiring capacity is so large that it deviates from the I2C standard, and the rising waveform becomes distorted as shown in Fig. 1, causing communication errors. You need to be careful.

Can it be solved by adjusting the pull-up resistance?

Generally, if the rising waveform is not good, increase the pull-up current (decrease the pull-up resistance) to drive even if the wiring capacitance is large.

However, if the pull-up current is too large, the Low level will rise (pull-up current x parasitic resistance) as a side effect and may deviate from the VOL specification.

So, what should be done if the communication error cannot be avoided by adjusting the pull-up resistor?

Solutions that reduce communication errors

What can be done when you need to connect to a backplane like a communication device or when I cannot avoid a communication error due to a parasitic capacitance such as connecting the boards with a flat cable and performing I2C bus communication?

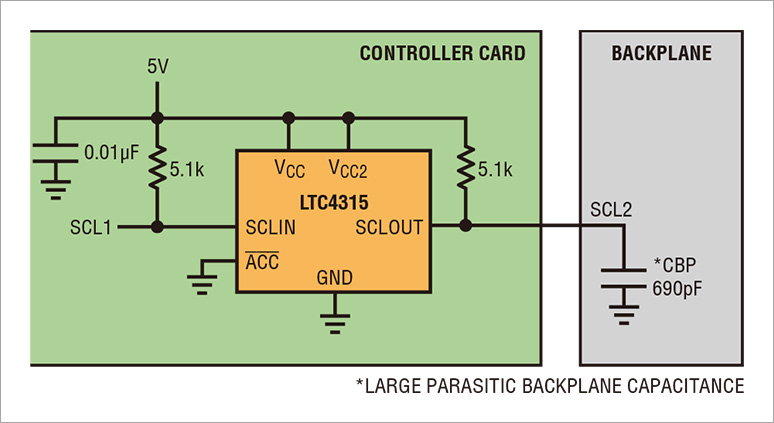

If the parasitic capacitance is not compliant, use Analog Devices’ I2C bus buffer product as a workaround.

LTC4315 has a Rise Time Accelerator feature, so it can improve the slow rising waveform.

By placing LTC4315 on the controller board as shown in Figure 3, it is possible to communicate normally even when connected to the backplane.

LTC 4315 is an essential product for I2C bus communication, which solves the problem of large parasitic capacitance between boards (devices).

For more information:

WeChat

WeChat

FPGA WeChat Platform

FPGA WeChat Platform

LinkedIn

LinkedIn