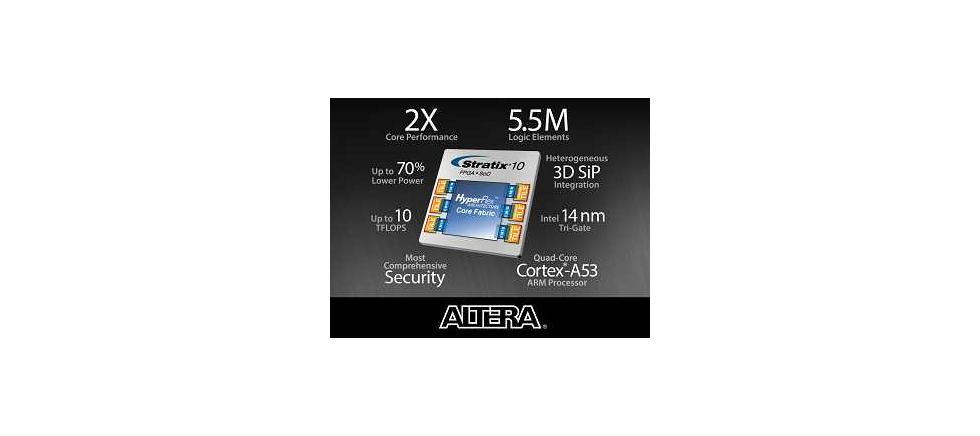

Altera Reveals Stratix 10 Innovations Enabling the Industry's Fastest and Highest Capacity FPGAs and SoCs

性能提高2倍,達到550萬個邏輯單元, 異質架構3D系統級封裝整合,以及最全面的安全功能

2015年6月9日,台灣——Altera公司(Nasdaq:ALTR)今天發佈其Stratix® 10 FPGA和SoC架構和產品細節,這一種下一代高階可程式化邏輯元件在性能、整合度、密度和安全特性方面實現全面突破。 Stratix 10 FPGA和SoC採用了Altera革命性的HyperFlex™ FPGA架構,由Intel® 14 nm三閘極製程技術製造,核心性能是前一代FPGA的2倍,是業界性能最好、密度最高、具有先進的嵌入式處理功能的FPGA,與GPU級別浮點運算性能和異質架構3D SiP整合特性相結合,可支援Altera客戶解決下一代通訊、資料中心、軍事、物聯網基礎設施和高性能運算系統中所遇到的設計挑戰。 Altera市場資深副總裁Danny Biran評論表示:「我們的Stratix 10 FPGA和SoC在業界具有無與倫比的功能,Stratix 10 FPGA和SoC可支援客戶在以往採用FPGA時所無法想像的創新方式來設計其系統。」

HyperFlex架構的「暫存器無處不在」方法

Stratix 10 FPGA和SoC是第一款採用公司的HyperFlex新架構的Altera元件,這是FPGA業界十多年來最顯著的架構創新。HyperFlex架構結合Intel 14 nm三閘極製程的全製程節點優勢,核心邏輯頻率比競爭對手的下一代高階FPGA高2倍。 HyperFlex架構在所有核心互聯佈線段上導入了暫存器,使得Stratix 10 FPGA和SoC能夠受益於成熟可靠的性能增強設計方法,例如暫存器重新定時、管線和其他設計最佳化方法,這些設計方法在傳統的FPGA架構中是不可能實現的。HyperFlex架構幫助設計人員避免了關鍵通路和佈線延時,其設計能夠迅速達到時序收斂。核心邏輯性能提高2倍後,不需要很寬的資料通路,也不會因為時鐘偏移導致需要採用特殊設計結構,大幅地提高了元件利用率,降低了功率消耗。HyperFlex架構支援高性能設計的降低邏輯面積要求,功率消耗進而降低了70%。請瀏覽www.altera.com/hyperflex,以瞭解更詳細的資訊。

異質架構3D系統級封裝整合的新時代

Stratix 10 FPGA和SoC系列的所有型號都採用了異質架構3D SiP整合技術,高效經濟的整合高密度單顆FPGA核心架構(高達550萬個邏輯單元),以及其他先進的零組件,進而提高了Stratix 10 FPGA和SoC的可擴展性和靈活性。單顆核心架構避免了使用多個FPGA晶片來提高密度的競爭同質架構元件的連接問題。Altera的異質架構SiP整合技術是透過使用Intel的專用嵌入式多晶片互聯橋接(EMIB,Embedded Multi-die Interconnect Bridge)技術實現的,與採用仲介層架構的方法相比,進一步提高了性能,降低了複雜度和成本,增強了訊號完整性。 初次發佈的Stratix 10元件將使用EMIB來整合高速序列收發器和通訊協定模塊以及單顆核心邏輯。透過異質架構3D SiP方法實現高速通訊協定和收發器,Altera將能夠快速交付Stratix 10元件型號,來滿足不斷發展的市場需求。例如,使用異質架構3D SiP整合技術為Stratix 10元件提供了途徑來實現更高的收發器速率(56 Gbps)、新出現的調變格式(PAM-4)、通訊標準(PCIe Gen4、多埠乙太網路),以及類比和寬頻記憶體等其他功能。 所有密度範圍的Stratix 10系列型號都將會整合64位元ARM®四核心Cortex®-A53硬式核心處理器系統(HPS),具有豐富的周邊特性,包括系統記憶體管理單元、外部記憶體控制器,以及高速通訊介面等。隨著Stratix 10 SoC的推出,Altera是唯一提供高階SoC FPGA的供應商,進一步增強了其業界領先地位。這一種通用運算平臺具有優異的適應能力、性能、功率效益、系統整合和設計效能,適用於多種高性能應用。設計人員可以在高性能系統中使用Stratix 10 SoC來實現硬體視覺化,增加管理和監控功能,例如,加速預先處理、遠端更新和除錯、配置,以及系統性能監控等。

全面的安全功能增強了對設計的保護

在高性能FPGA中,Stratix 10 FPGA和SoC將會具有業界最全面的安全功能。其核心是創新的安全設計管理器(SDM,Secure Design Manager),支援採用區塊架構的認證和加密、多因素認證和實體不可複製功能(PUF,physically unclonable function)技術。Altera與Athena集團以及IntrinsicID合作,為Stratix 10 FPGA和SoC提供了世界級加密加速和PUF IP。Stratix 10 FPGA和SoC的多層安全和分區IP保護特性非常優異,這一個級別的安全特性使得該元件成為軍事、雲端安全和物聯網(IoT)基礎設施應用的理想解決方案。

適用於Stratix 10 FPGA和SoC的Enpirion PowerSoC

Stratix 10 FPGA和SoC由Altera的系列Enpirion PowerSoC電源解決方案提供供電。Enpirion PowerSoC經過最佳化滿足了嚴格的性能和功率要求,在最小的接腳佈局中提高了效率。

業界數百萬LE設計能夠以最短時間達到時序收斂

Altera的Quartus® II中的Spectra-Q新引擎經過設計發揮了HyperFlex架構的性能、功率和面積優勢,同時還提高了Stratix 10 FPGA和SoC設計人員的效能,產品能夠更迅速面市。Quartus II軟體的新功能將編譯時間縮短了8倍,提供通用、快速追蹤設計輸入和置入式IP整合特性,支援OpenCL和其他高階設計流程,延續了Altera軟體的領先優勢。關於Spectra-Q引擎的更多資訊,請瀏覽www.altera.com/spectraq。

Stratix 10 FPGA和SoC技術規範:

- 單顆晶片上有550萬個邏輯單元

- 異質架構3D SiP整合技術結合了具有高速收發器的FPGA架構

- 144個收發器的序列頻寬是前一代的4倍

- 運作在1.5 GHz的64位元四核心ARM Cortex-A53硬式核心處理器子系統

- 硬式核心浮點DSP支援單精確度運作高達10 TFLOPS運算性能

- 安全元件管理器:全面的高性能FPGA安全功能

- 業界領先的單事件干擾(SEU)偵測和消除功能

- 從Arria® 10 FPGA和SoC的接腳佈局相容移植途徑

- Altera Enpirion電源解決方案提高了功率效益,節省了電路板面積

- Intel 14 nm三閘極製程技術

供貨資訊

客戶現在可以使用快速前向編譯性能評估工具開始其Stratix 10設計。將於2015年秋天提供Stratix 10 FPGA和SoC工程樣品。嵌入式軟體發展人員可以採用Mentor Graphics提供的SoC虛擬平臺來加速Stratix 10 SoC嵌入式軟體的開發。關於Stratix 10 FPGA和SoC產品的詳細資訊,請聯繫您當地的Altera業務代表,或者瀏覽www.altera.com/stratix10。

Altera簡介

Altera®的可程式設計解決方案幫助電子系統設計人員快速、高效率地實現創新,突出產品優勢,贏得市場競爭。Altera提供FPGA、SoC、CPLD產品,以及電源解決方案等互補技術,為全世界的客戶提供高價值解決方案。請瀏覽http://www.altera.com。

ALTERA、ARRIA、CYCLONE、ENPIRION、MAX、MEGACORE、NIOS、QUARTUS和STRATIX等字詞和標記是Altera公司的商標,在美國專利和商標事務所以及其他國家進行了註冊。其他被認定為商標或者服務標記的字詞和標識的所有權屬於其各自持有者,已於www.altera.com/about/legal.html對此進行了解釋。