Clock Buffer 你選對了嗎?專用型與通用型規格知多少?

現今的電子電路設計從個人電子計算機到消費型電子產品或工業級的高性能網絡通信系統,時鐘頻率緩衝器與時鐘分頻器是各個系統中時鐘的分配與建構的理想選擇。

以時鐘緩衝器來說,瑞薩電子推出一系列符合PCIe Gen1-Gen5標準與JESD204B/C相容的專用型產品以及更多支持LVPECL、LVDS、HCSL、CML、HSTL 或LVCMOS 輸入輸出的通用型緩衝器可供選擇。甚至有一些緩衝器可用於混合輸出信號。

而元件的選擇,你會注意那些規格或參數呢?

我會注意以下幾個地方:

1. 電源架構是單電源還是雙電源?

2. 輸入與輸出的訊號類型是何種差分或單端訊號,電壓與訊號的擺幅是多少?

甚至抖動與延遲都是我們需要特別注意的地方。

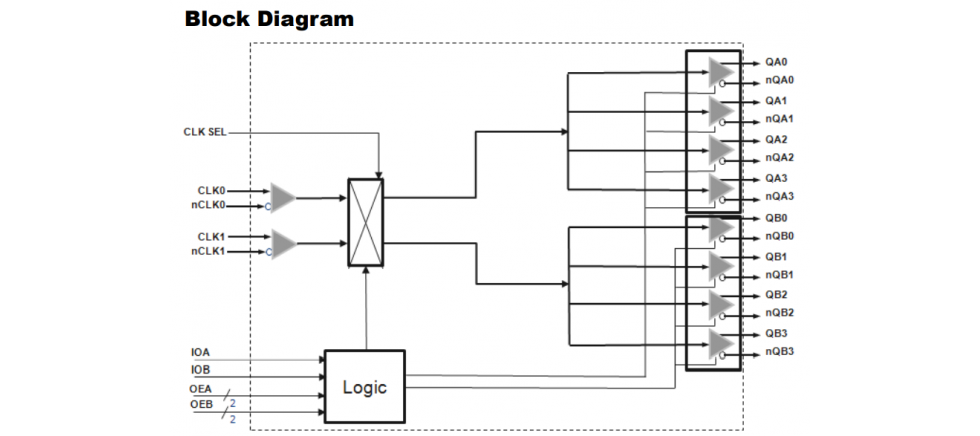

以下就以瑞薩電子可支持混和信號輸出的通用型元器件 8P791208 時鐘緩衝器為例,作規格的介紹:

功能

- 輸入頻率範圍從 1PPS 到 700MHz

- 兩個差分輸入支持LVPECL、LVDS、HCSL或LVCMOS參考時鐘輸入

- 生成8個差分或16個LVCMOS輸出

- 輸出排列成兩組,每組4個輸出

- 由選擇引腳 (CLK_SEL)控制哪個輸入驅動哪組輸出

- 輸出類型可以選擇LVPECL、LVDS或2xLVCMOS

- 每組支持3.3V、2.5V或1.8V輸出

- LVCMOS輸出限制為最大125MHz並支持3.3V、2.5V、1.8V或1.5V的擺幅

- 獨立輸出啟用與類型選擇

- 156.25MHz時,-158dBc/Hz的低噪聲輸出

- 3.3V、2.5V或1.8V內核電壓供應

- -40 oC至85oC 環境溫度

- 無鉛 ( RoHS 6 ) QFN-32 ( 5 x 5 mm ) 封裝

圖一

圖一

電源

首先,緩衝器的電壓供給通常是單電源或雙電源之一。單電源架構就是僅提供 3.3V、2.5V或1.8單一電源。雙重供給分為核心供應和輸出供應,這為電壓轉換提供了優勢,也改善了輸入和輸出之間的隔離度。雙重電源供應的權衡是,它需要分別針對不同的電源進行濾波,如8P791208 支持雙重電壓模式。

輸入與輸出

時鐘緩衝器可以接受單端訊號或差分訊號,也可以兩者兼有。單端訊號型態最常見的是CMOS。差分訊號型態你會看到LVDS、CML、HCSL、LVPECL

的應用。與差分輸入相比,單端輸入需要更少的終止電組與更簡單的PCB訊號佈線,但是缺乏噪音免疫能力,容易將來自其他信號或地面噪聲耦合到信號路徑上,從而降低性能。差分信號就其性質而言,會排斥常見模式的雜訊與偶次諧波。

單端時鐘訊號的重要規格輸入包括表示邏輯高的VIH和邏輯低的VIL。兩者之間的距離越大,就表示對噪聲雜訊事件的容忍度就越高。

對於差分時鐘輸入也有類似的重要規格,即差分輸入電壓峰到峰值Vp-p或VCMR,即common mode 電壓。 它設定了邏輯0和邏輯1之間的電壓值。

單端時鐘訊號的重要規格輸入包括表示邏輯高的VIH和邏輯低的VIL。兩者之間的距離越大,就表示對噪聲雜訊事件的容忍度就越高。

對於差分時鐘輸入也有類似的重要規格,即差分輸入電壓峰到峰值Vp-p或VCMR,即common mode 電壓。 它設定了邏輯0和邏輯1之間的電壓值。

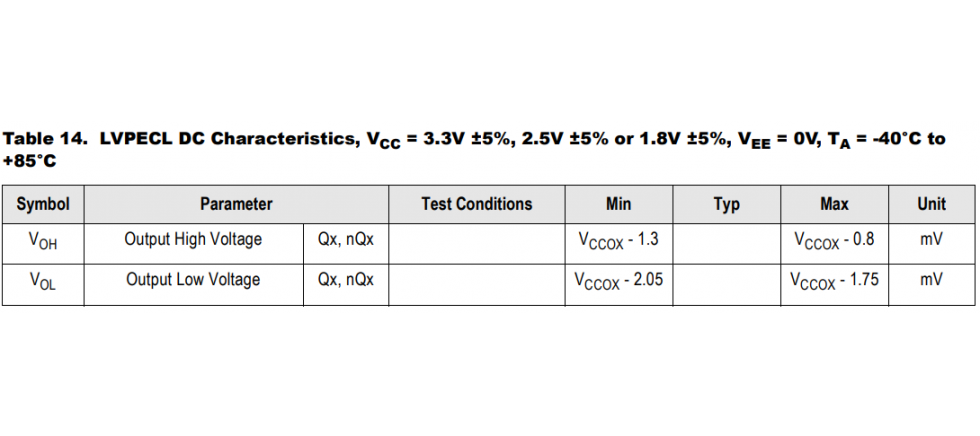

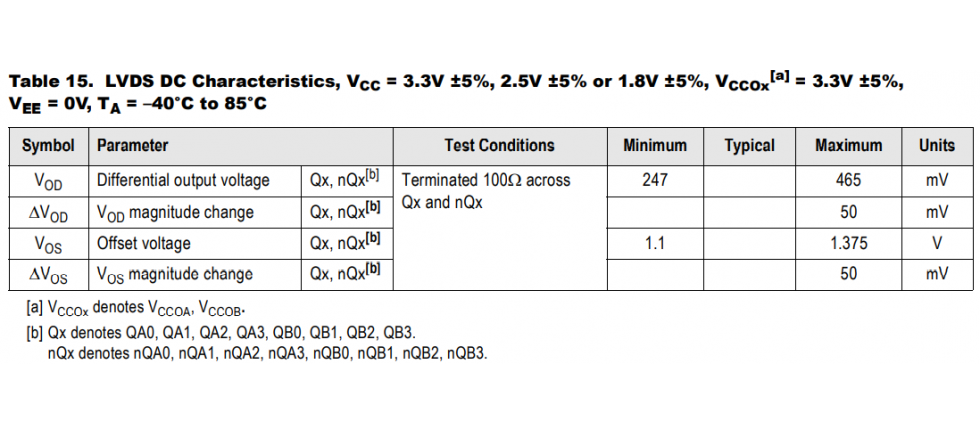

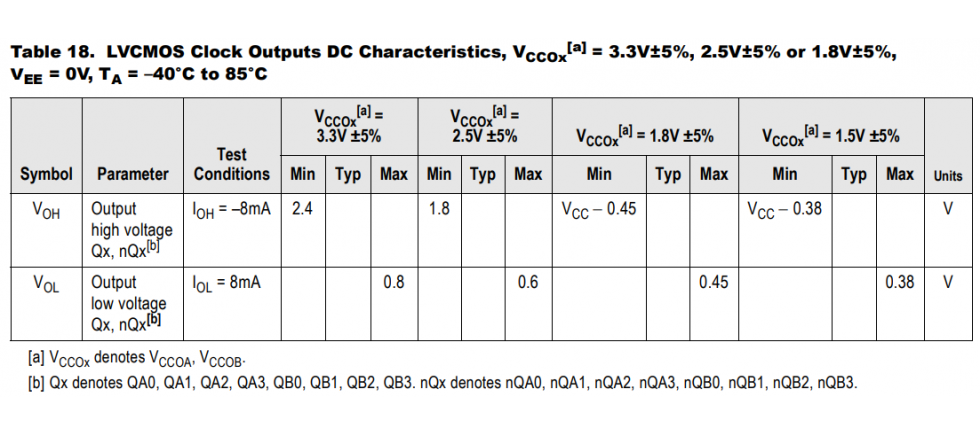

單端時鐘輸出的重要規格是VOH輸出高壓、VOL輸出低電壓值。對於差分時鐘緩衝器輸出,也具有VOD差分訊號輸出電壓。 與輸入一樣,也定義了common mode輸出參考電壓,即VOS。 對於這兩種輸出類型,您都需要注意輸出阻抗與終端匹配阻抗,如下表所示 ( 摘錄於8P791208 datasheet )

表一

表一

表二

表二

表三

表三

輸出信號擺幅與common mode電壓

對於 CMOS 單端信號輸出,此處的VOH與VOL表示不同的輸出邏輯。邏輯1必須大於最小的VOH ,而邏輯0必須小於最大的VOL,中間電壓是VDD的一半。

對於 LVDS 差分信號類型,通常是以 1.2 V為common mode電壓與峰對峰值訊號擺幅 700mV,並以地面電壓為參考點。

對於LVPECL差分信號,甚至提供更高的擺動幅度與低阻抗,輸出位準以VDD為參考點。實際線路設計請參考瑞薩電子相關文件。

HCSL 時鐘緩衝器現在越來越受歡迎,用於分發PCI Express信號。 8P791208提供方便且快速的交流耦合來支持HCSL 時鐘緩衝。Renesas 更提供全系列符合PCIe Gen1-Gen5規範的緩衝器與分頻器,產品應用擴及Intel / AMD 及相關平台。

抖動與延遲

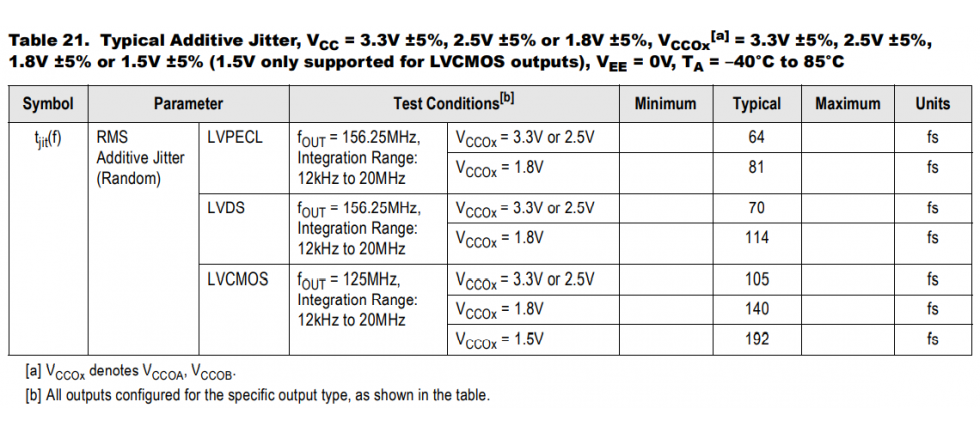

時鐘緩衝器輸出的相位雜訊或相位噪聲(Phase noise)包含外部輸入階段雜訊與緩衝器本身所產生的相位雜訊。緩衝器本身所產生的雜訊主要由兩類型所組成,低頻偏移雜訊(Low frequency offset noise)和熱雜訊 ( thermal noise wideband)。低頻偏移雜訊通常與閃爍雜訊相關(flicker noise),有時又稱為1/f雜訊,因為它的雜訊功率與頻率成反比。

另一個重要的雜訊類型是熱雜訊,其具有均勻的雜訊功率頻譜,與電阻、電晶體及其他相關元件有關。緩衝器的抖動與相位噪聲靈敏度因訊號擺幅和架構而有所不同。較高的輸入擺幅能夠得到比較好的訊號完整性。而較高的輸入訊號上升斜率( Slew rate ) 也有助於降低相位噪聲的抖動。較高的訊號輸出斜率也能得到較好的相位噪聲性能。而較高的輸出負載也會降低相位噪聲的性能。

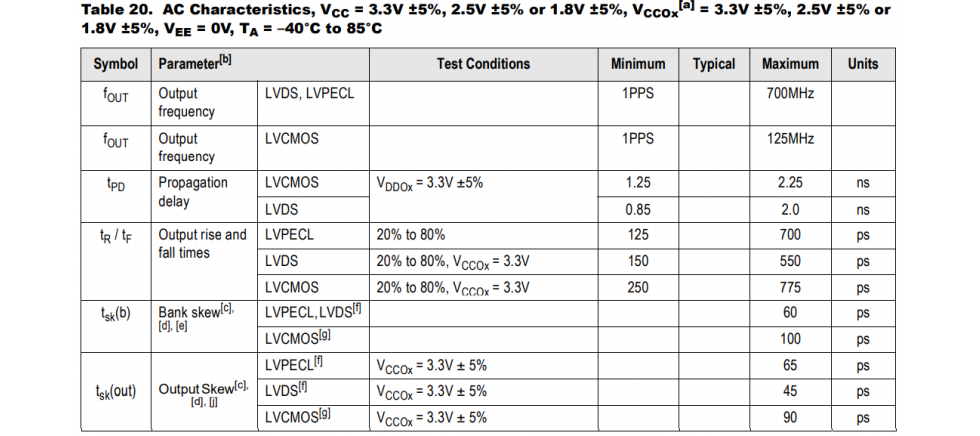

從輸入到輸出的傳播延遲tPD 對於系統正時至關重要。更高的傳播延遲可能導致更長的設定時間或限制最大操作頻率。而緩衝器的低輸出偏斜(Output Skew) 對所有輸出波形具有良好的對齊性,對於需要將精確時鐘分發到並行的多個位置,以確保並行的多個裝置能夠同步,必須要關注的參數。

表四

表四

表四

表四

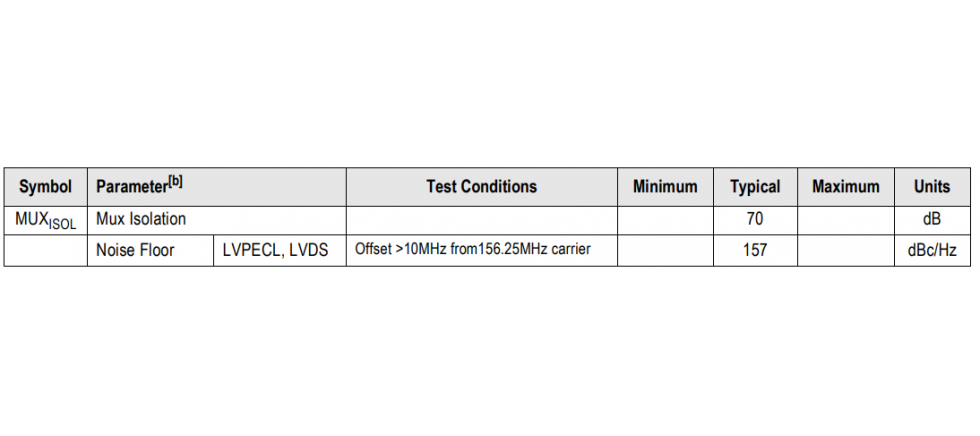

8P791208 也提供了多工器的隔離度訊息,讓有不同輸入需求的設計人員有更多的選擇。

表六

表六

功耗

緩衝器的功率消耗取決於多個參數與使用架構。包括操作頻率、輸出負載、VDD、工作中的輸出數,都可以發揮作用。功耗也取決於緩衝器中使用的架構類型即電流或電壓模式,電壓模式架構會隨著操作頻率的增加而增加,CMOS 緩衝器就是一個例子。電流模式架構(如LVPECL)的功耗通常獨立於頻率。

參考文獻

- TEXAS INSTRUMENTS, 1.3 TI Precision Labs - Clocks and Timing: Clock Buffer Key Parameters and Specifications, https://training.ti.com/ti-precision-labs-clocks-and-timing-clock-buffer-key-parameters-and-specifications

- Renesas, Low Additive Jitter 2:8 Buffer with CMOS / Differential Outputs, https://www.renesas.com/tw/en/document/dst/8p791208-datasheet?language=en&r=194661