使用Intel® Arria 10 實現 Delay Chain 方案

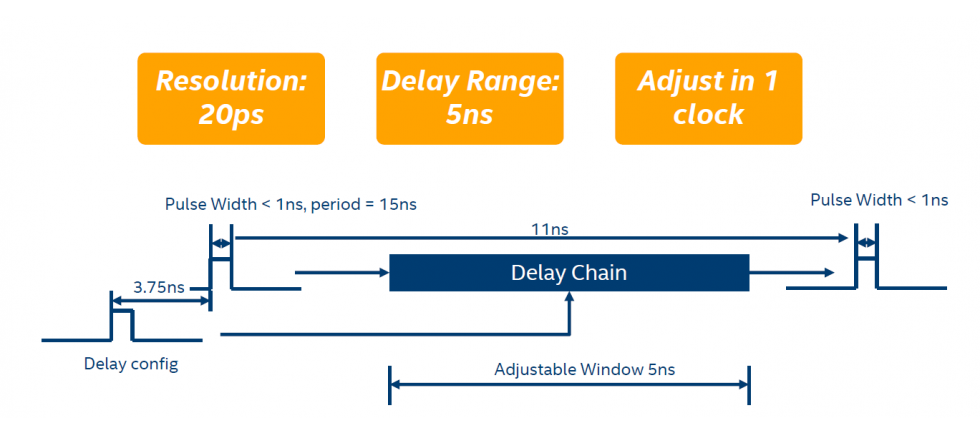

一般FPGA設計I/O Delay 都是基於時鐘的同步邏輯所設計的,信號會被clock 重新編排,同步Delay的精度取決於時鐘的頻率。如圖一,在某些測試應用領域需要產生Pico second等級的測試脈衝,同時要求有Pico second級的訊號Delay精度。

圖一、客戶需求的功能

圖一、客戶需求的功能

這時候傳統的同步邏輯設計就達不到應用的要求,需要採用非同步邏輯的方式設計,但是非同步邏輯的最大缺點是一致性無法控制,如果是通過FPGA內部的來實現信號的傳輸延遲,那麼每次compiler結果的差異性都會比較大,並且很難去分析。

如果能在FPGA中找到一種固定的路徑資源,作為Pico second等級測試脈衝的路徑,同時這個路徑資源又可以等分成很多級,每一級都可以把傳輸信號引出來,這樣就可以達成信號傳輸路徑,且整個傳輸路徑的延遲可測、可調整,那麼就能符合測試需求了。

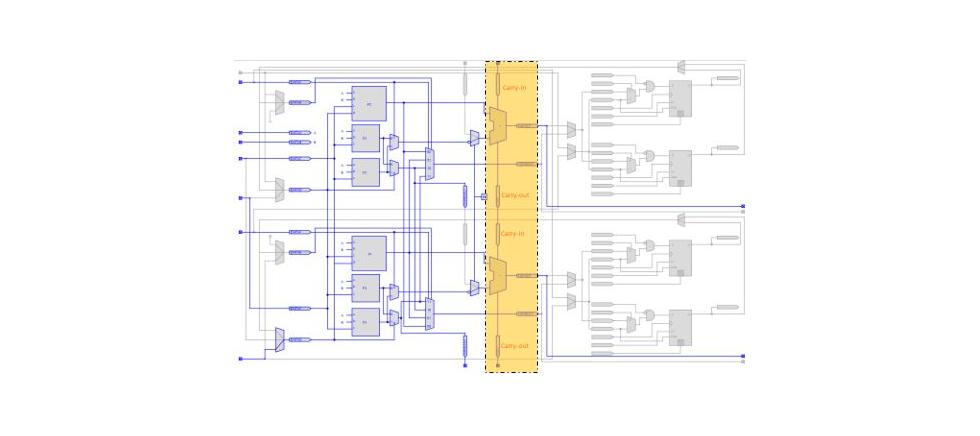

圖二、Arria 10 內部線路

圖二、Arria 10 內部線路

以圖二來說是使用Quartus Prime 上的Chip Planner Tool來看到Arria 10內部ALM架構,一個ALM 是由兩個4輸入 1 輸出的LUT和 四個3輸入 1輸出的LUT組成8 輸入的LUT、兩個硬體加法器和進位線路、以及四個暫存器所組成的。

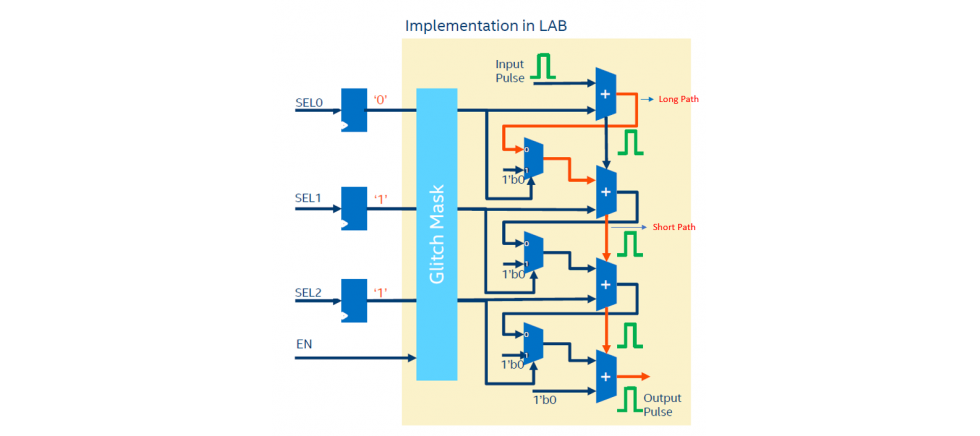

圖三、簡單三個Node實現Delay Chain

圖三、簡單三個Node實現Delay Chain

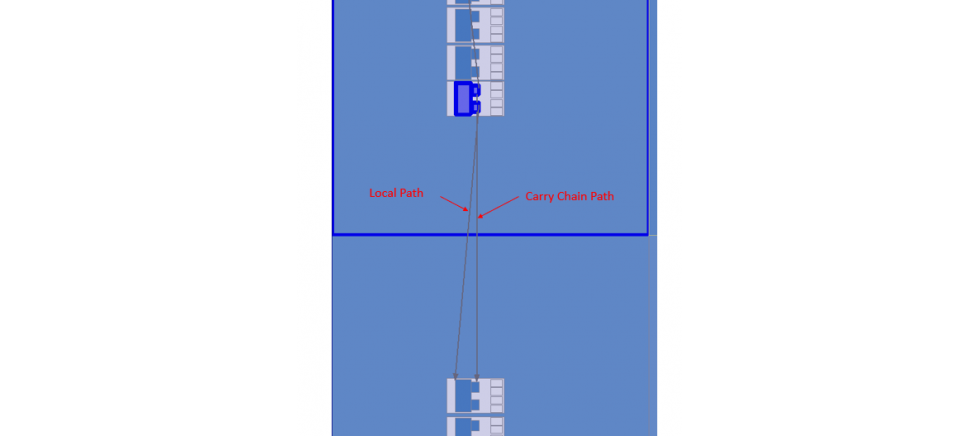

圖三是一個簡單三個Node 的Delay Chain 範例。其利用每個硬體的加法器上實現的功能是 a + b + cin = sum_out,而a 和 b 是加法器上的data, sum_out 則是加法後的結果輸出到下一級或是輸出的訊號、cin是上一級的進位輸入、cout 是與下一級的cin 相連;經過驗證跨LAB(一個LAB內含10個ALM)之後的進位路徑cin和cout也是直接連到下一級的,不經過其他的線路,如圖四。

圖四、跨不同LAB時的Carry Chain 與Local Path

圖四、跨不同LAB時的Carry Chain 與Local Path

因此Node 有兩個輸出的路徑,短的是Carry Chain interconnect Delay,長的是Local interconnect with LAB Delay,由SEL [2 : 0] 來做不同路徑的調整,0是選擇Long Path,1是選擇Short Path,最多有八個不同delay 的組合,Glitch Mask 用來避免SEL 的MUX 所產生glitch訊號 , 由這樣的設計方案,就不會因同步時鐘而將訊號整形,同時也達到Pico second級的訊號Delay精度了。

更