USB4:高速互連的新標準浪潮與工程挑戰解析

引言

近年來高速資料的傳輸需求與日俱增,USB4 的導入已成為高速傳輸應用連接市場近年最重要的變革之一。根據市場調查機構與供應鏈觀察,PC、NoteBook、Docking Station 與高速外接 GPU/SSD 的需求成為帶動 USB4 滲透率的主要力量。

隨著雲端內容創作、AI PC、8K 媒體剪輯等高資料量應用加速普及,用戶對高速、低延遲與高功率傳輸通道的需求急速上升。USB4 則被視為「單一高速互連」的重要關鍵:它整合了 USB、PCIe、DisplayPort 多協定傳輸能力,並維持與 USB3/USB2 的回溯相容,使其成為高效能周邊的主流高速介面。

Thunderbolt 與 USB4 迷思

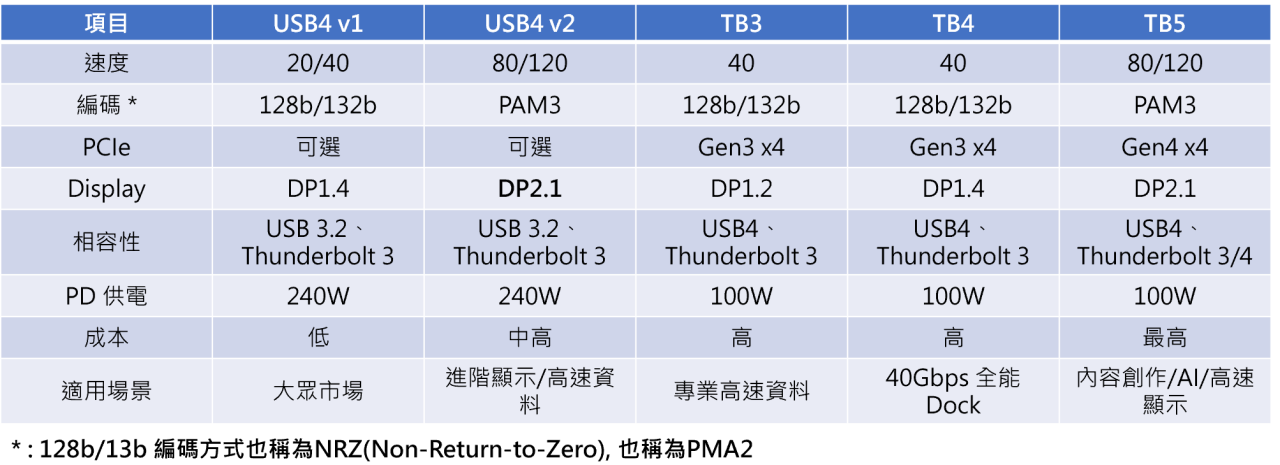

在高速 I/O 介面進入 40Gbps 世代後,「USB4」與「Thunderbolt」成為兩條最常被並列比較的規格。它們看似競爭,實際上卻有著深度交集。

當時源於Intel 將 Thunderbolt 3 相關技術授權給 USB-IF,讓 USB4 與Thunderbolt 能採用相同的傳輸協定 (tunneling protocol) 將不同訊號別的訊號整合透過一條Type C cable 做傳輸,另外擁有可達 40Gbps 的高速傳輸能力,然而,USB4 和 Thunderbolt 之間仍有細微但重要的區別。如表一所示。

- USB4 強調: 開放、彈性、普及

- Thunderbolt 強調: 效能保證、穩定、專業

表一

表一

USB4 技術電氣層架構概觀

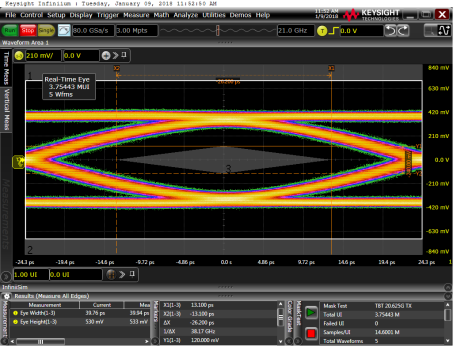

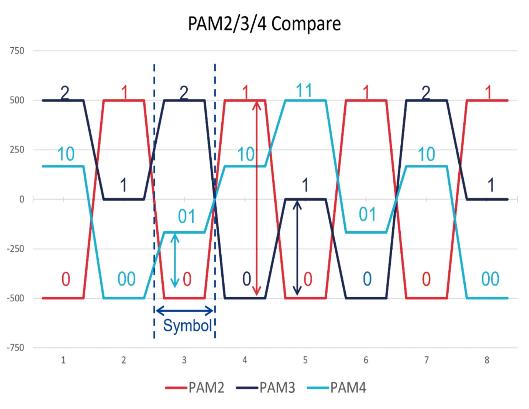

USB4 V1剛問世時, 電氣層採取的編碼方式是NRZ( Non-Return-to-Zero) 訊號編碼,也稱作Pulse Amplitude Modulation 2-level(PAM_2)訊號,二進制的編碼,使用高低準位來代表邏輯1與0。NRZ每個Symbol可以傳送1個位元(log2 2=1)。利用2個電壓狀態進行傳輸,所以會形成一個眼圖,如圖一所示。

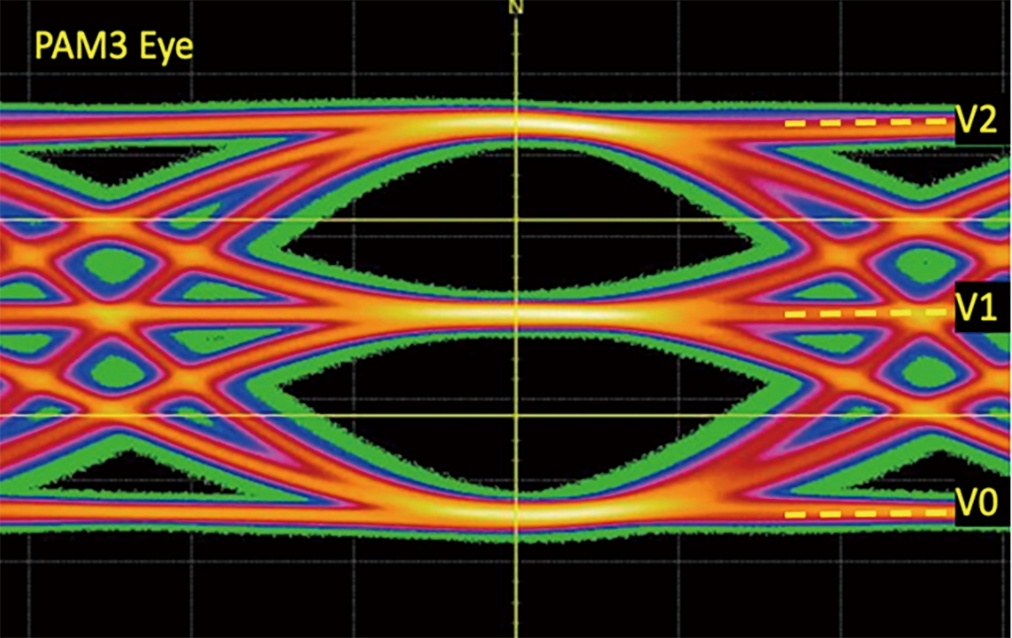

當USB IF 宣告USB4演進至V2規格時,其傳輸率也提高到80Gbps(對稱傳輸) 與 120Gbps(非對稱傳輸)領域,電氣層採取的編碼方式則由原來的NRZ改變為PMA_3,利用3階脈衝振幅調變,三進制的編碼,通常以-1、0、+1或者0、1、2來表示Ternary (三元)值,PAM_3每個Symbol可以傳送1.58個位元(log2 3=1.58)。利用三電壓狀態進行傳輸,所以會形成上下兩個圖二所示。 PAM_2(NRZ), PAM_3, PAM_3,取樣比較如圖三所示。

圖一

圖一

圖二

圖二

圖三

圖三

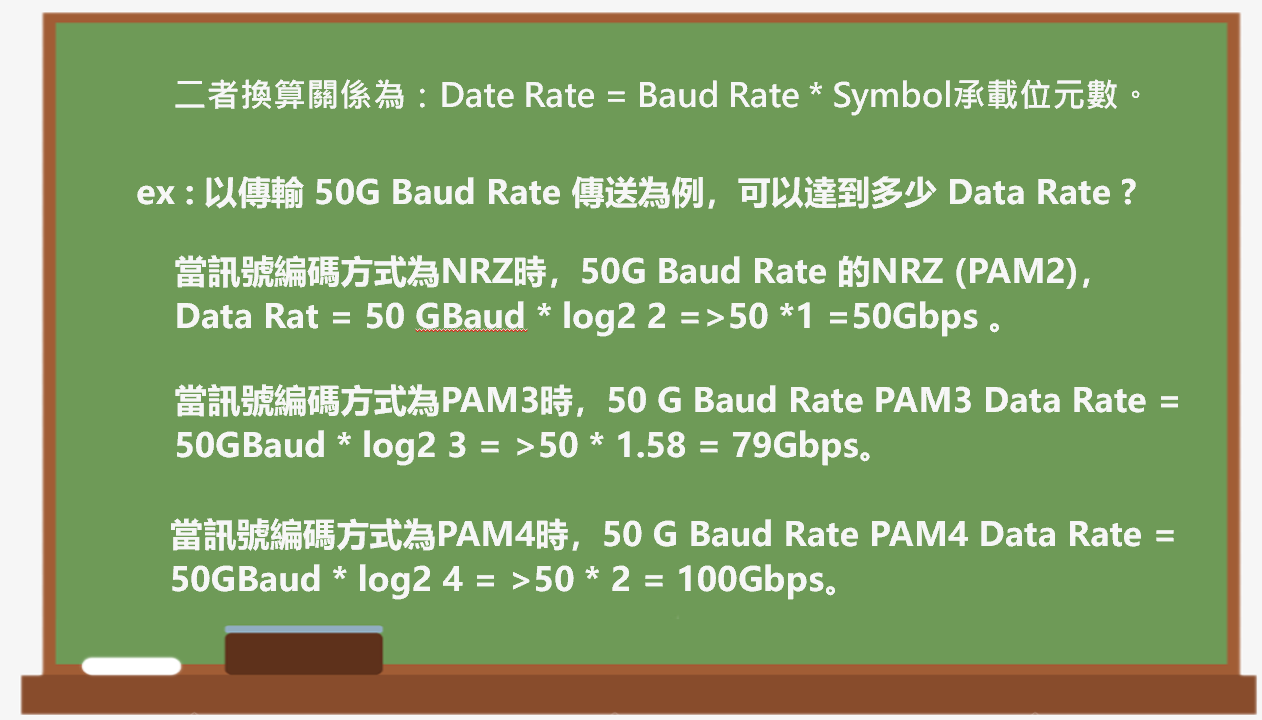

高速介面資料傳輸速度Date Rate,通常以bps(bit per second)來表示單位,是指每秒傳輸的位元數。但市場上常見的單位有分為Data Rate與Baud Rate,這所指的都是頻傳輸率的單位,其二者換算關係為:Date Rate = Baud Rate * Symbol承載位元數。

從下方就可以了解隨著訊號編碼的改變,傳輸相同Baud Rate,可以得到不同的Data Rate。這也是USB4 V1演進到V2 傳輸率提升最大的技術點。

EX:以傳輸50G Baud Rate 資料在不同的編碼環境下,所取得的Data Rate各是多少?如圖四所示。

圖四

圖四

USB4 工程設計挑戰

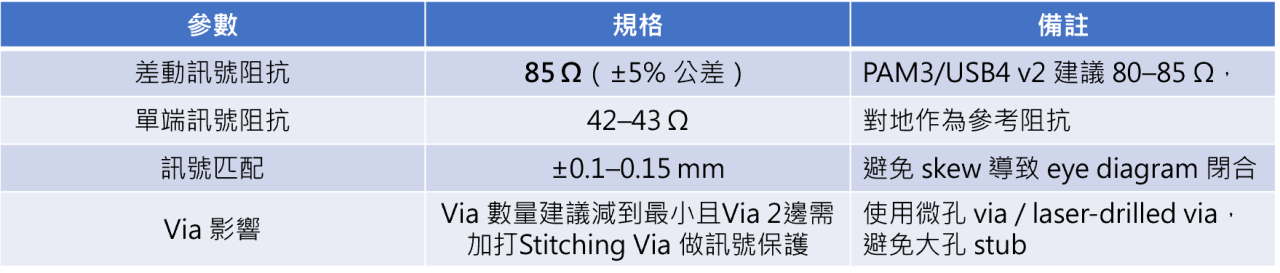

USB4 電氣編碼採用PAM_3,傳輸率則提升到80Gbps / 120Gbps(非對稱),所以在PCB設計上要求相對與USB3.2 10Gbps PCB設計更加嚴格,下表二所示,為USB4 PCB design相關規範。

表二

表二

挑戰_1 : PCB材質選擇 (主IC端→Type C connector.)

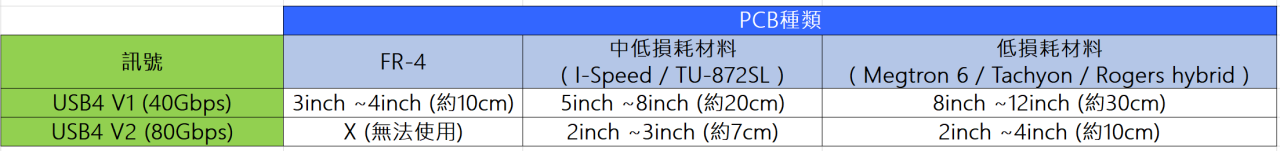

1-1. PCB材料的選擇在USB4應用上相當的關鍵,如果選用錯誤的材料,將可能導致USB4 function 受到限制甚至無法正常工作。如表三所示。

表三

表三

挑戰_2 : USB Connector 擺放與PCB佈線重點

2-1. USB Connector 的種類有 SMD Type 與 DIP Type,以下針對此兩種形式的Connector , 在佈局時提列注意事項:

- SMD Type: 為維持impedance 連續,儘避免有 Through-Hole (穿孔) 在信號的腳pin上。如果需要搭配REDRIVER / RETIMER應用,會建議擺放位置在與SMD Type C Connector pin 同一面,如此就可以將高速訊號走線直出不經過Through-Hole。

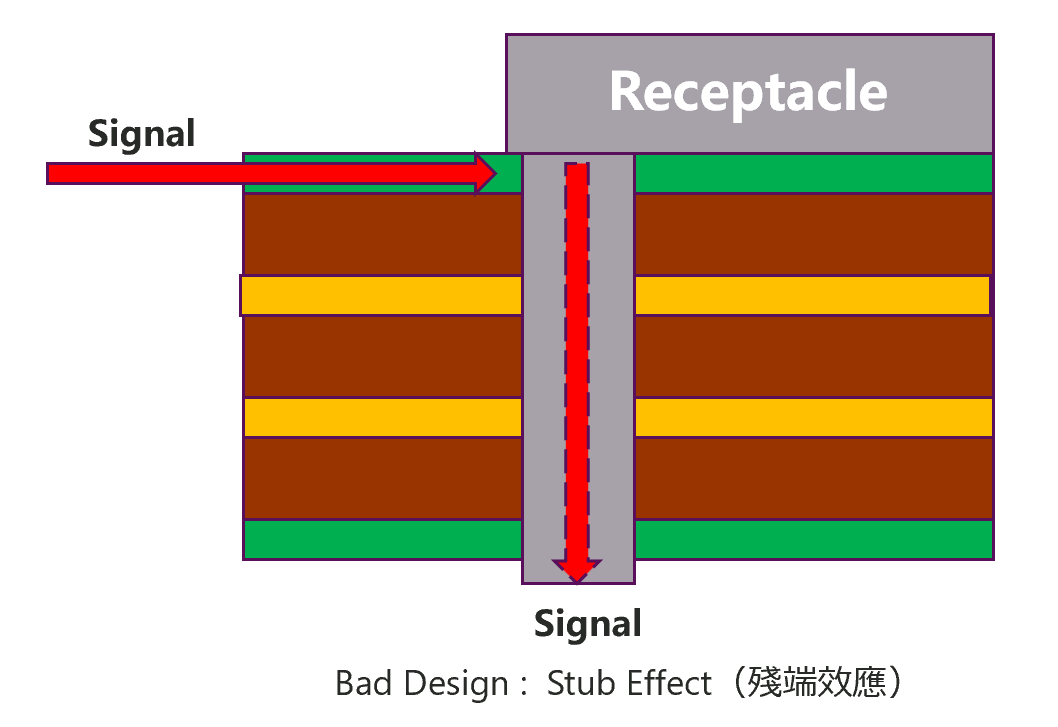

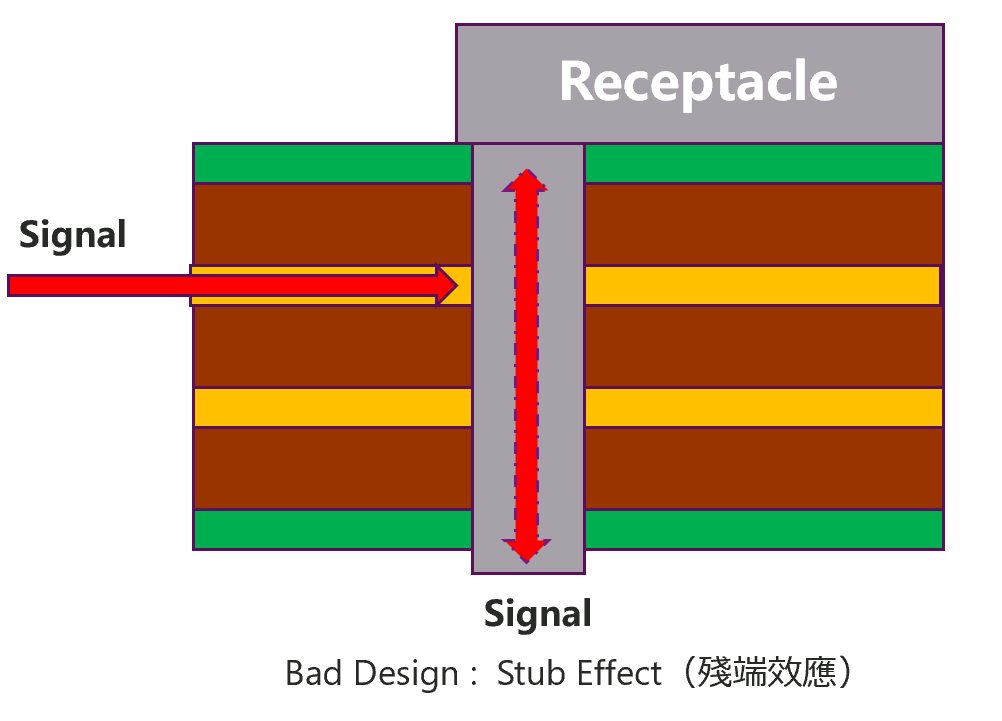

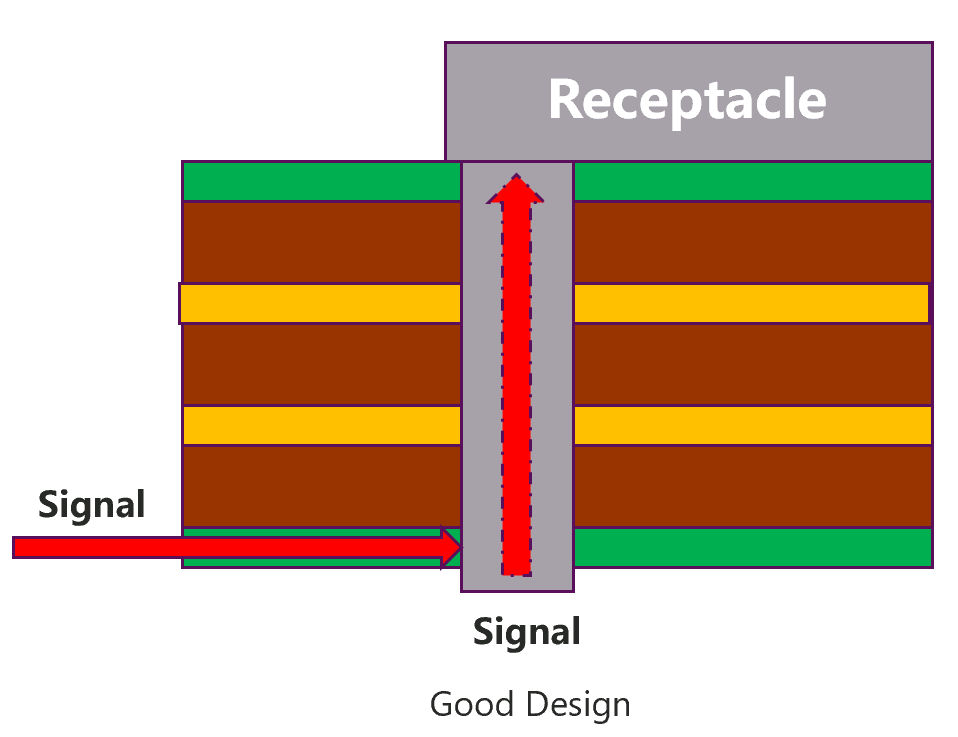

- DIP Type: 為了讓高速訊號輸出走線直接連結DIP腳的末端,為了不產生Stub Effect的問題, 應用REDRIVER / RETIMERR則須放在與DIP connector 的相反側以期達到沒有Stub Effect最佳效果。然而設計者常因機構料件的原因,無法順利依據此方式時,請參考圖五所示。其中建議相關替代方案,來避免Stub Effect的問題。

圖五

圖五

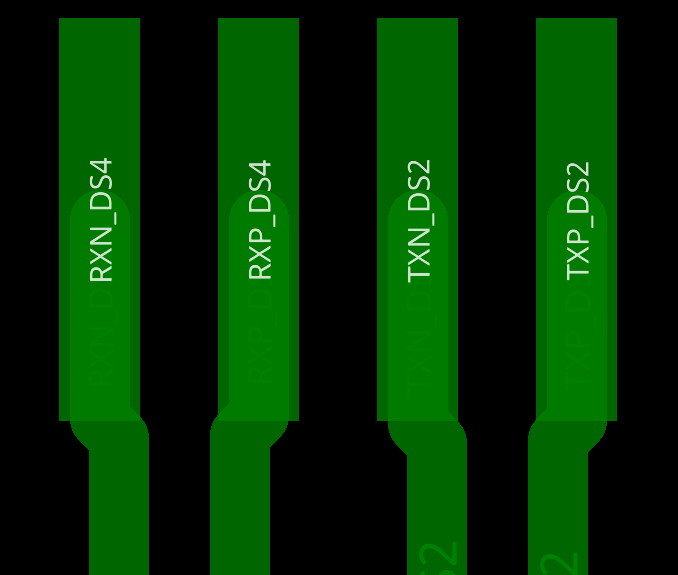

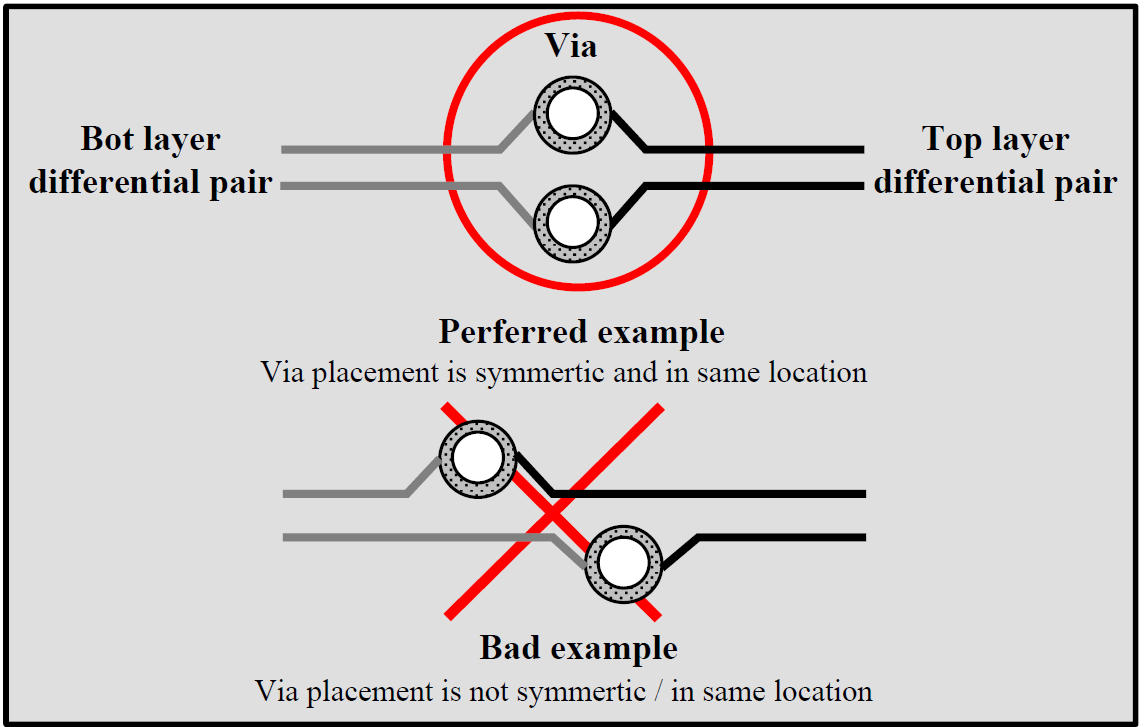

2-2. Top / Bottom layer:無論進/出PIN or 進出Via差動訊號必需對走線方式佈線。如圖六所示。

圖六

圖六

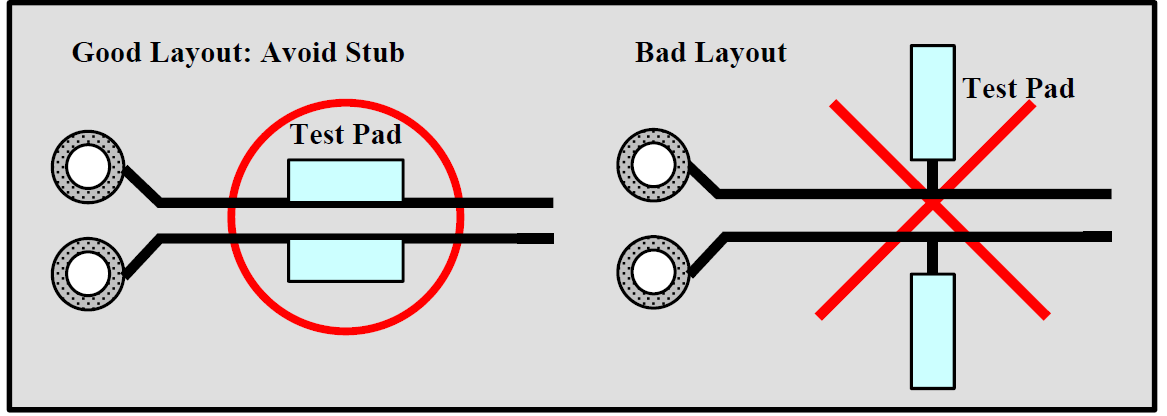

2-3. 在訊號線上要放置相關測試點做為debug使用,其擺放位置需與訊號平行,不宜額外拉出trace。如圖七所示。

圖七

圖七

2-4. 必須保持GND(參考層)完正性。

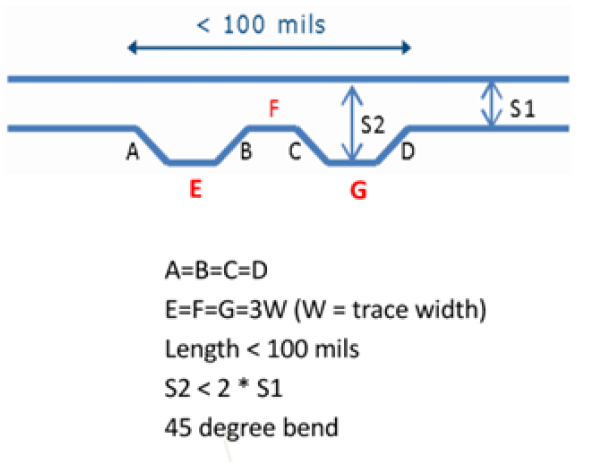

2-5. 蛇線,僅用於長度匹配,同一線段不宜連續多次使用,其次數越少越好。如圖八所示。

圖八

圖八

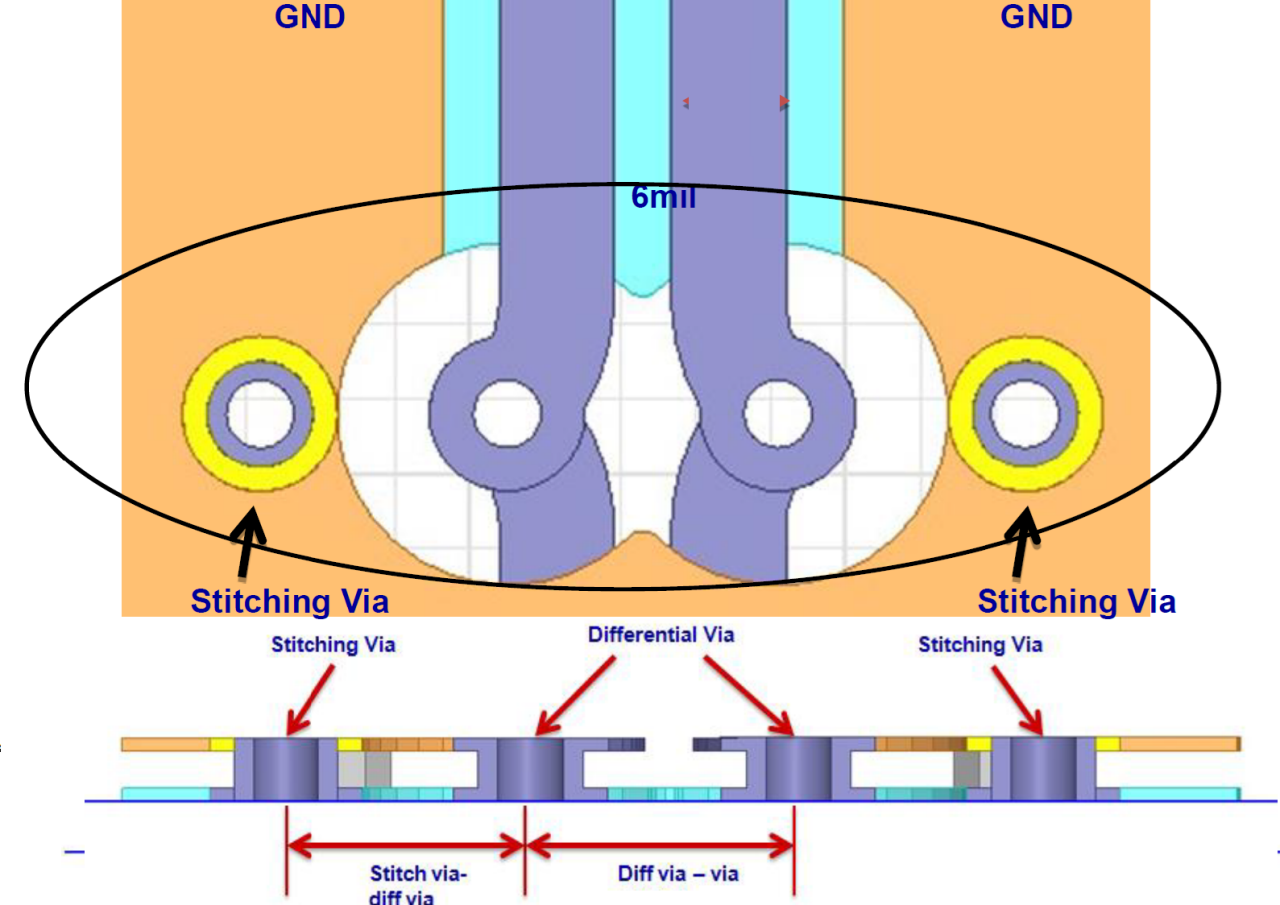

2-6. Via 儘量越少越好,如果有必要,需在訊號線的Via 2旁各加打Stitching Via做為保護。如圖九所示。

圖九

圖九

挑戰_3 : USB4主要料件的擺放與訊號延伸料件的相對位置

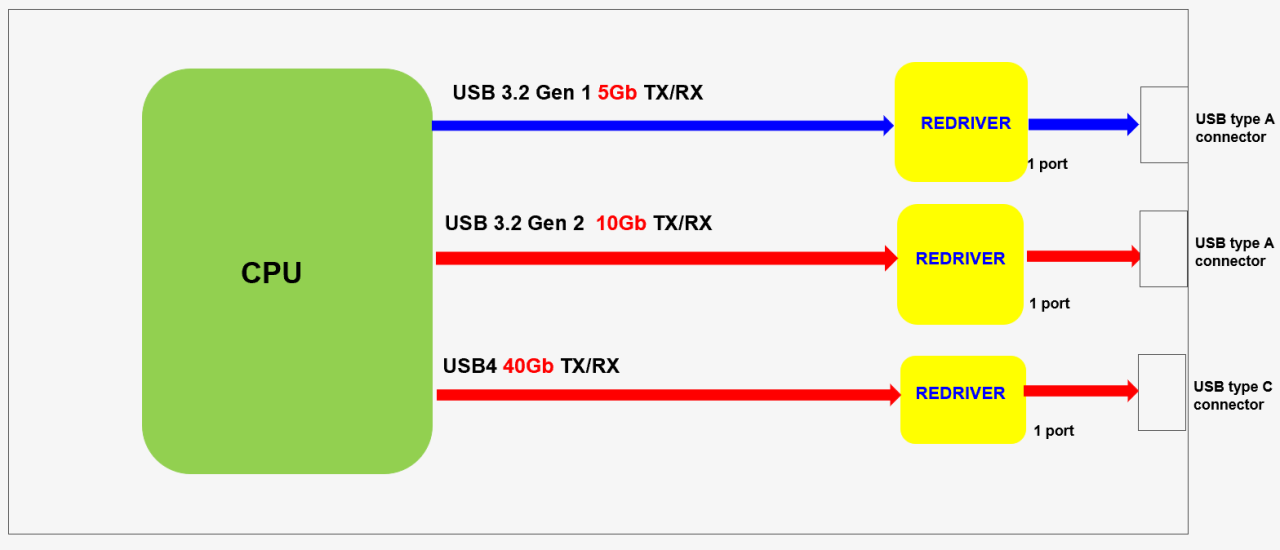

3-1. 因各家產品需求的不同,USB4 主IC擺放的位置也會有所不同,且到device or Connector Total trace length一樣也是會有差異,所以通常USB4的產品設計一般大多都會搭配RETIMER or REDRIVER一起應用,如此將有助於USB4訊號品質與完整性。擺放方式如圖十所示。

圖十

圖十

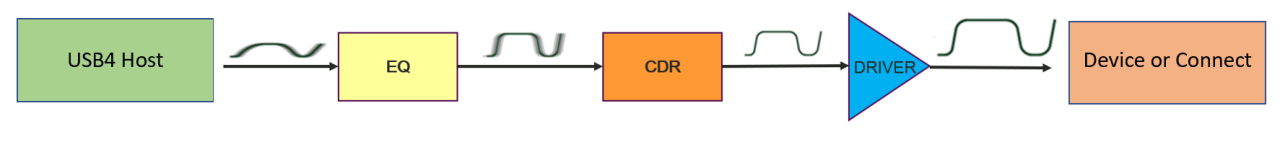

3-2. 搭配RETIMER應用,RETIMER主要包含兩個功能。一個是對信號進行均衡,另一個則是對有確定性抖動和隨機性抖動的數據時鐘信號進行修復,從而輸出一個乾淨的信號給後端裝置使用。RETIMER功能簡易示意圖,如圖十一所示。

圖十一

圖十一

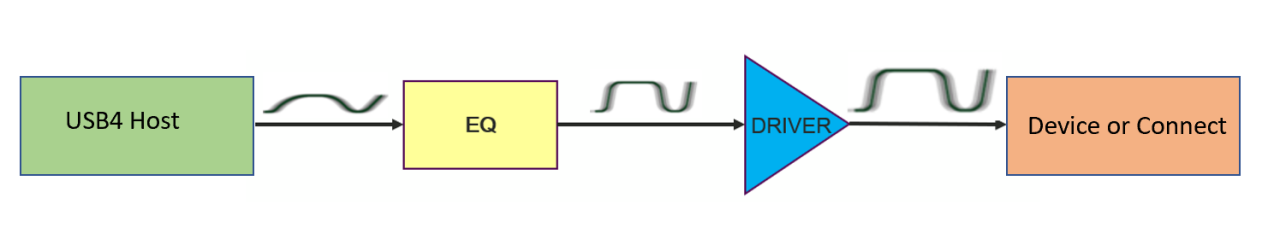

3-3. 搭配REDEIVER應用,REDRIVER則是通過使用均衡器(EQ=EQUALIZTION)以及預加重控制(PRE- EMPHASIS)技術,讓REDRIVER可以補償與矯正傳輸端上訊號的損失,並在接收端上恢復訊號完整性。因此可以在訊號發射端產生滿足傳送損耗的可靠訊號、以減少訊號錯誤率的眼圖 。REDRIVER功能簡易示意圖如圖十二所示。

圖十二

圖十二

結語

USB4 正在快速重塑 AI、Server、PC 與高速周邊產業的架構。對系統設計者、IC 設計公司、主機板 OEM、線材/Connector 製造商與測試工程師而言,它不僅代表更高的頻寬,更是一個必須跨越協定整合、訊號完整度、PD 功率管理與相容性測試的全新工程挑戰。在 2025 之後,USB4 將成為筆電與周邊設備的新常態,而 USB4 V2更將推動下一波高速互連革命。

茂綸在這個高速傳輸應用的浪潮中也不缺席。憑藉著對於市場上應用及需求的瞭解並搭配茂綸完整產品線的支援,無論是USB4 HUB、REDRIVER、PD3.1 PD controller、Power端的buck boost…等。

茂綸具備專業的團隊替客戶提供完整的Solution與支術支援,讓客戶能在最短時間內取得成果,達到雙贏的目標。