半導體晶片的心臟:時脈產生器

科技的蓬勃發展都仰賴於半導體晶片技術的創新與先進製程技術的研發,不只提高了晶片效能更大幅的縮小了電晶體尺寸,在各個高科技領域如AI、機器人、無人機、電動車、資料中心、工業自動化等相關應用,都受益於半導體晶片技術的提升所致,然而要驅動任何晶片的核心其實是時脈產生器,它就像是半導體晶片的心臟一般,提供一個穩定且固定的頻率讓半導體晶片可以當作為標準的參考信號,用來計算或處理相關資料的傳輸。

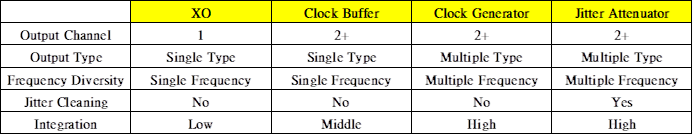

時脈產生器的種類可以大致分為4大類(圖1),其中以XO(Crystal Oscillator)與Clock Buffer在設計上較為簡單,但是整合度較差,比較適用於單一頻率需求的晶片使用,而Clock Generator與Jitter Attenuator的高整合度則較適用於複雜系統且需要多種不同時脈頻率需求的晶片使用。

(圖1)

(圖1)

在時脈線路設計上很重要的一個部分是Termination matching(終端匹配),Termination matching主要是優化時脈傳輸線的訊號品質,避免時脈傳輸線產生EMI(電磁干擾)或是Crosstalk(串音干擾)影響到系統的穩定度,可以大幅的提升整體系統的穩定性及可靠度。

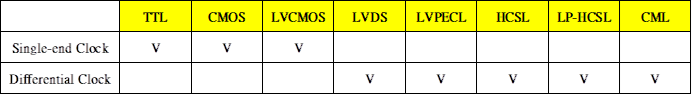

時脈種類: (圖2)

- TTL (Transistor-Transistor Logic 電晶體對電晶體邏輯)

- CMOS (Complementary Metal-Oxide-Semiconductor 互補金氧半導體)

- LVCMOS (Low Voltage Complementary Metal-Oxide-Semiconductor 低電壓互補金氧半導體)

- LVDS (Low-Voltage Differential Signaling 低電壓差分信號)

- LVPECL (Low-voltage positive emitter-coupled logic 低電壓正極耦合邏輯)

- HCSL (High-Speed Current Steering Logic 高速電流控制邏輯)

- LP-HCSL (Low Power High-Speed Current Steering Logic 低功率高速電流控制邏輯)

- CML (Current Mode Logic 電流模式邏輯)

(圖2)

(圖2)

TTL / CMOS / LVCMOS這些是屬於Single-end Clock(單端時脈)訊號,通常是用於低速頻率訊號使用。TTL輸出不能直接驅動CMOS輸入使用,CMOS相對於TTL有了更大的雜訊容許能力,輸入阻抗遠大於TTL輸入阻抗。相對應於3.3V的LVTTL type,發展出了LVCMOS type,LVCMOS可以直接與LVTTL相互驅動使用。

Differential Clock(差動時脈)相較於Single-end Clock(單端時脈)擁有更好的雜訊抑制能力以及更高頻率的時脈訊號使用,高頻時脈可以高達數百MHz。

不同種類的Differential Clock無法直接相互驅動使用,需要透過外部的線路做時脈訊號的轉換才能相互的驅動使用。

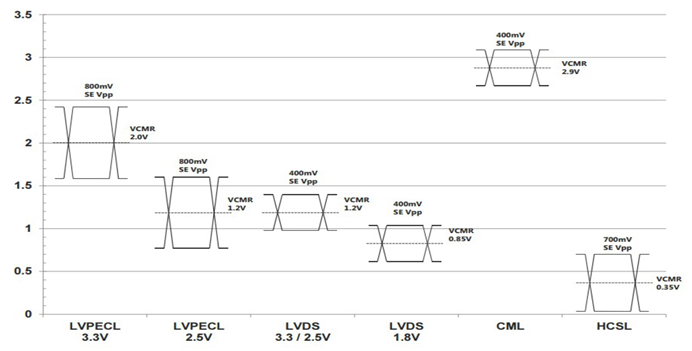

不同的種類的Differential Clock它們的Vcm(Common-mode Voltage 參考電壓)跟Swing (振幅)大小是不同的(圖3),要讓驅動端與接收端可以正常的相互對接,需要確保兩端的Vcm準位是相同的,以及驅動端的高電位振幅與低電位振幅必須是在接收端可以接受的振幅範圍內,簡單來說就是接收端的振幅範圍必須大於驅動端的振幅能力(圖4)。

(圖3)

(圖3)

(圖4)

(圖4)

以下我們針對不同的Differential clock type來做說明。

LVDS (Low-Voltage Differential Signaling 低電壓差分信號)在Differential clock的應用層面上非常的廣泛,由4顆電晶體組成,LVDS的Vcm是1.2V,經由固定3.5mA的電流源驅動,由於LVDS接收端的高輸入阻抗特性,幾乎全部的3.5mA驅動電流源都流經100 ohm(歐姆)的匹配電阻,所以在接收端會產生350mV的電壓振幅大小(圖5)。

(圖5)

(圖5)

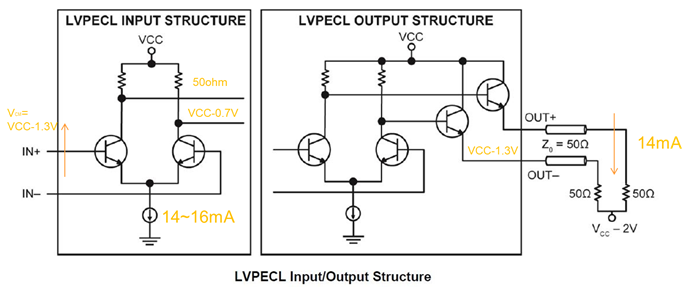

LVPECL (Low-voltage positive emitter-coupled logic 低電壓正極耦合邏輯)的Vcm是VCC-1.3V,內部是14mA ~ 16mA的電流源驅動,流經50 ohm(歐姆)的匹配電阻,所以在輸出端會產生大約700mV ~ 800mV的電壓振幅大小(圖6)。

(圖6)

(圖6)

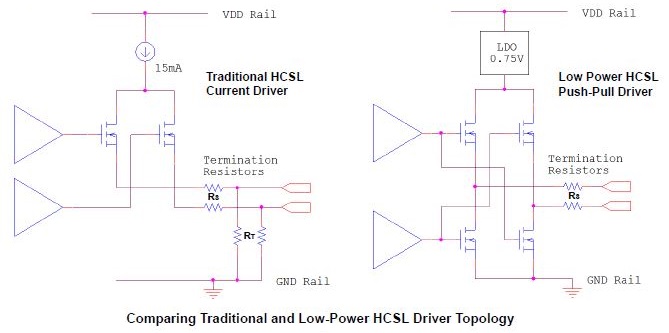

HCSL (High-Speed Current Steering Logic 高速電流控制邏輯) 的Vcm是0.35V,內部是14mA的電流源驅動,流經50 ohm(歐姆)的匹配電阻,所以在輸出端會產生700mV的電壓振幅大小(圖7)。

(圖7)

(圖7)

LP-HCSL (Low Power High-Speed Current Steering Logic 低功率高速電流控制邏輯)的Vcm與Swing跟HCSL架構都相同,傳統的HCSL驅動是透過控制差分對中的14mA~16mA 電流源,其電源功率消耗約3.3V x 14mA ~ 16mA = 46.2mW ~ 52.8W,LP-HCSL則是採用Push Pull(推挽式)的電壓驅動模式,其電流功率消耗只有約4 ~ 5mA,大幅的降低了功率損耗以及電路板板材面積,另外LP-HCSL擁有可以驅動較長走線的特性(圖8)。

(圖8)

(圖8)

CML (Current Mode Logic 電流模式邏輯)的Vcm為VCC-0.2V,外部是8mA的電流源驅動,流經50 ohm(歐姆)的匹配電阻,所以在輸出端會產生400mV的電壓振幅大小(圖9)。

(圖9)

(圖9)

在相同的Differential clock type情況下驅動端與接收端可以直接的對接就是所謂的DC Coupling(直流耦合)模式,但是如果驅動端與接收端是不同的Differential clock type情況下,就需要透過AC Coupling(交流耦合)模式,將驅動端的Vcm電壓移除,然後在接收端重新將Vcm電壓給加回來,使其Vcm符合接收端的規格。

以下是幾種常用的不同type的Differential clock轉換:

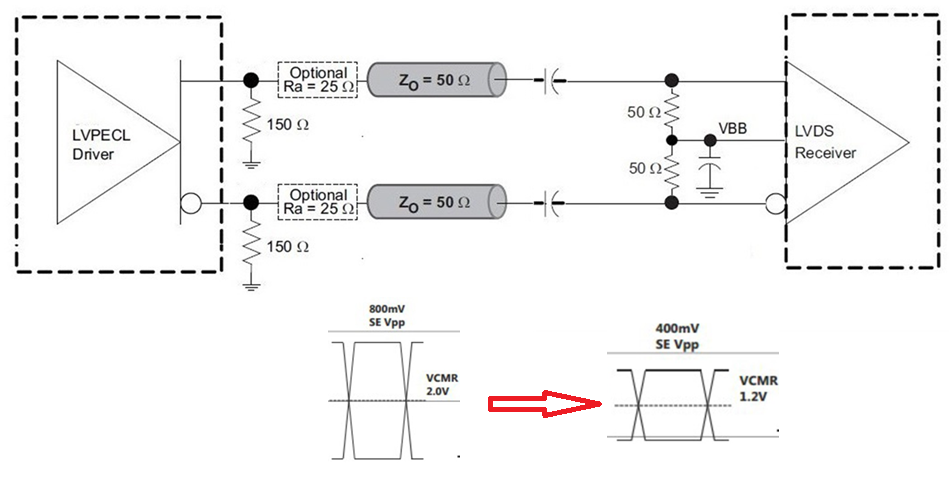

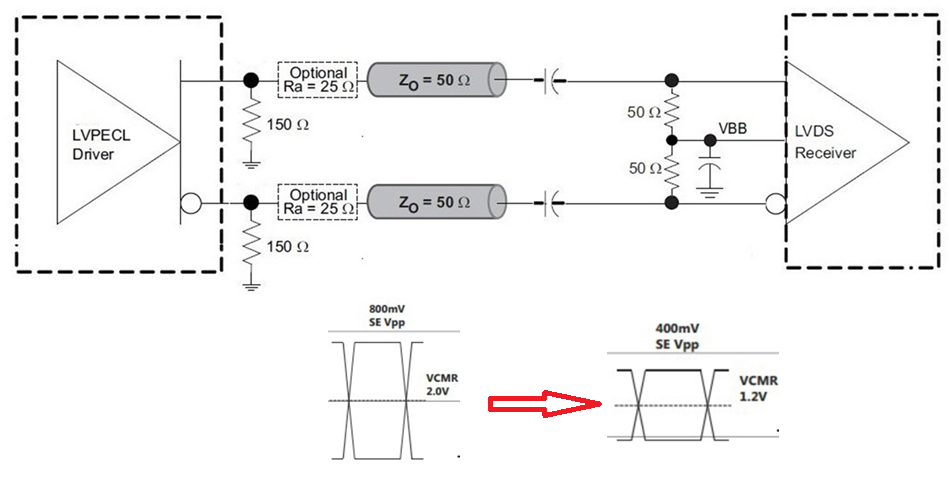

LVPECL to LVDS

LVPECL的Vcm是2V,Swing大小是800mV,Vcm的2V直流準位經過串聯電容後會被濾除只剩下Swing通過,接收端外部放置Re-bias電源與匹配電阻,使其規格符合LVDS規範(圖10)。

(圖10)

(圖10)

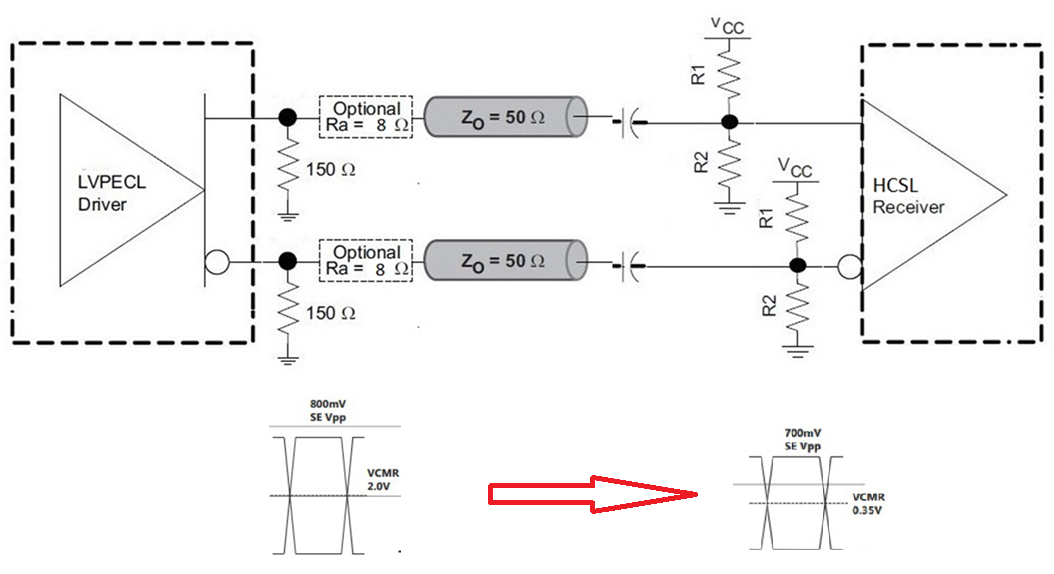

LVPECL to HCSL

LVPECL的Vcm是2V,Swing大小是800mV,Vcm的2V直流準位經過串聯電容後會被濾除只剩下Swing通過,接收端外部放置Re-bias電源與匹配電阻,使其規格符合HCSL規範(圖11)。

(圖11)

(圖11)

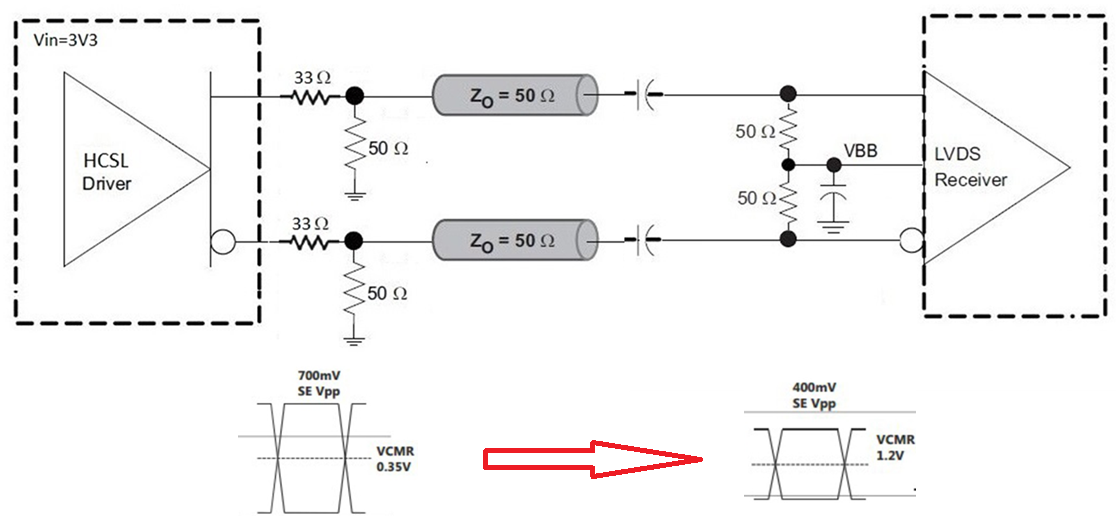

HCSL to LVDS

HCSL的Vcm是0.35V,Swing大小是700mV,Vcm的0.35V直流準位經過串聯電容後會被濾除只剩下Swing通過,接收端外部放置Re-bias電源與匹配電阻,使其規格符合LVDS規範(圖12)。

(圖12)

(圖12)

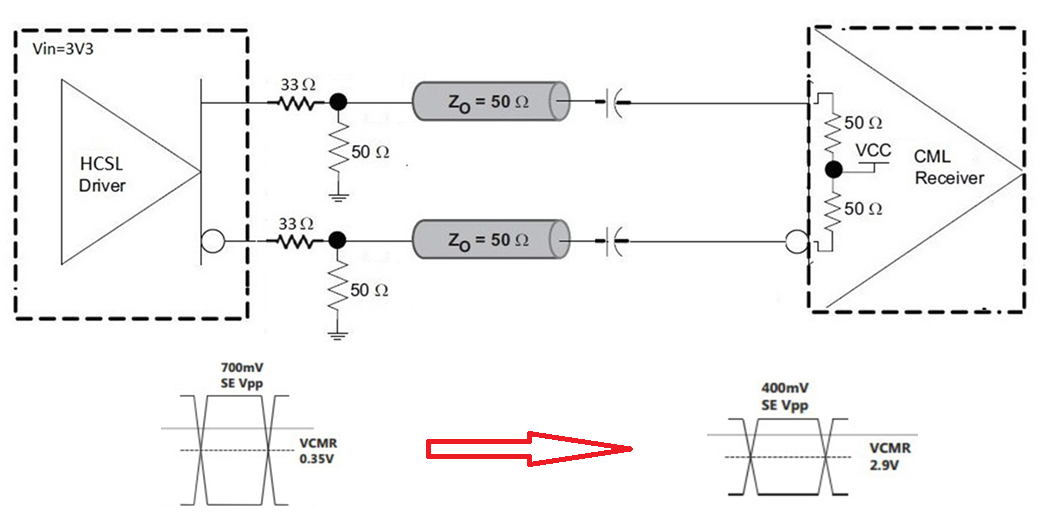

HCSL to CML

HCSL的Vcm是0.35V,Swing大小是700mV,Vcm的0.35V直流準位經過串聯電容後會被濾除只剩下Swing通過,接收端內部配置Re-bias電源與匹配電阻,使其規格符合CML規範(圖13)。

(圖13)

(圖13)

隨著AI、機器人、無人機、電動車、資料中心、工業自動化等相關應用的崛起,時脈線路在設計上也越來越被要求及重視,除了時脈種類、頻率以外,時脈相位抖動(Clock Phase Jitter)規格越低越好(0.1ps以下),輸出頻率穩定性的誤差、相位同步、頻率同步等規格都是在這些特定的應用上需要考量的。

茂綸所代理的瑞薩電子(Renesas)產品線提供了所有時脈產生器的完整方案,其中包含了硬體與軟體(IEEE 1588)的整合,在Time to Market的市場競爭下為客戶提供最優質的解決方案。