使用Intel FPGA實現V-by-One ® HS方案

Mpression – Macnica's Original Technology Brand Mpression品牌展示了Macnica集團公司提供全球客戶的解決方案和技術。 Mpression致力於研發FPGA, 處理器等關鍵技術,並提供IP, SW, HW等專業知識提供出色的解決方案,以下先幫大家介紹Mpression V-by-One® HS方案。

Mpression V-by-One® HS

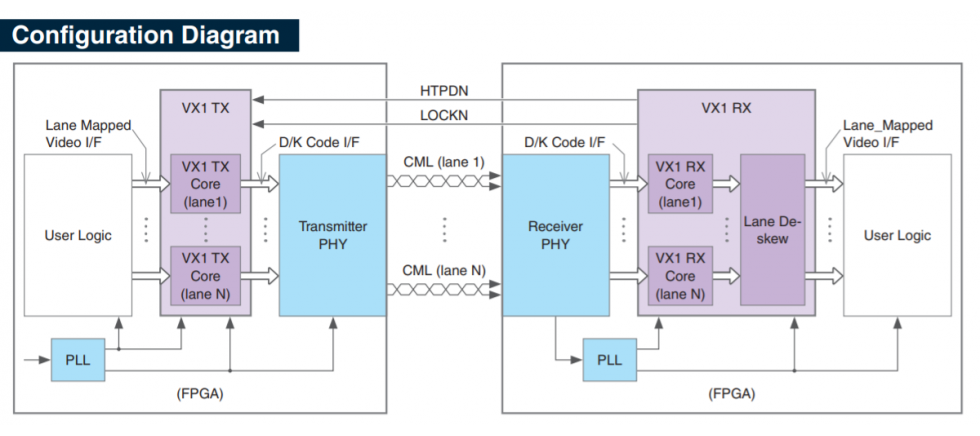

現代液晶電視具有大尺寸和高畫質的趨勢,而提升畫質的方式需要有更高frame rates和resolutions. 但是付出的代價就是造成Video Board和T-CON之間數據量大幅增加,傳統LVDS設計方式已經達到極限,此時就輪到V-by-One ® HS來取代LVDS. V-by-One ® HS是Thine Electronics為視頻設備開發的下一代高速接口技術的標準,主要是為了支持實現高速視頻接口技術的IP, 與傳統的LVDS接口相比,在Intel FPGA中實現V-by-One ® HS IP可以減少信號數量,從而大大降低了產品成本。 V-by-One ® HS IP具有兩種類型的IP, 一種類型是配備有V-by-One®HS發送器功能的 VX1 TX IP; 另一個是配備了V-by-One®HS接收器功能的VX1 RX IP 。

圖1

圖1

V-by-One ® HS的功能概述

- 可配置多達32條通道,每個通道最大傳輸速率為4 Gbps

- 支持自定義視頻格式以及 VESA、SMPTE 和其他標準化格式

- 映射視頻接口的有效數據的位寬可以設置為24位元,32位元或40位元

- D/K代碼接口的可配置位寬度:8位元,16位元或32位元

- VX1 RX IP支持De-skew功能

- VX1 TX IP支持Field Bet Generator,它會生成誤碼測試碼

- VX1 RX IP支持Field Bet Checker,它可以檢查接收到的比特錯誤測試碼中的錯誤。

Example Configuration (TX)

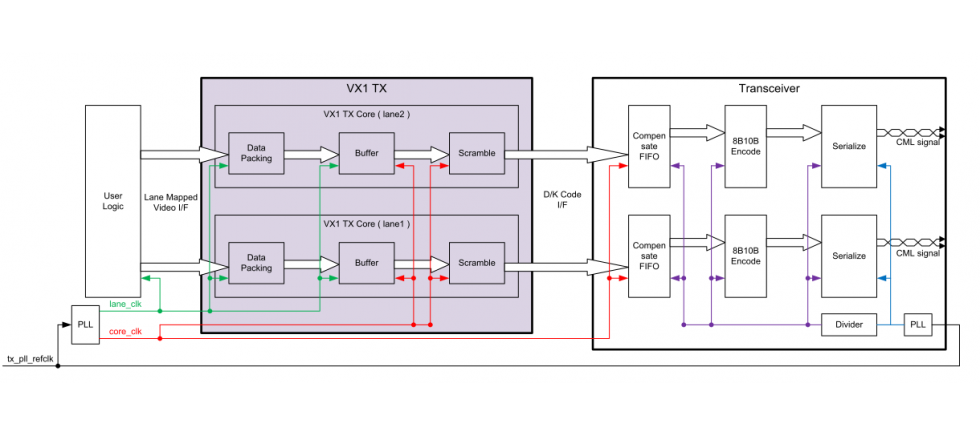

圖2顯示V-by-One®HS 發送器的示例框圖,其中如果使用兩個通道則連接 VX1 TX IP, User Logic, PLL和Transceiver. VX1 TX IP需要兩種clock(core_clk 和lane_clk),這些clock必須沒有頻率偏差。所以兩個clock會由PLL產生。

因此, User Logic和VX1 TX IP的連接包含lane_clk和Lane Mapped Video Interface。

圖2

圖2

範例:

對於Full HD 60p,byte_mode = 4byte,phy_mode = 4byte,傳輸速率可以計算如下:

[encoded total bit rate](bps) = [byte_mode](byte) × 8 × 10/8 × [pixel clock](Hz)

[encoded total bit-rate](bps) = 4 × 8 × 10/8 × 148.5 × 106

= 5,940 × 106(bps)

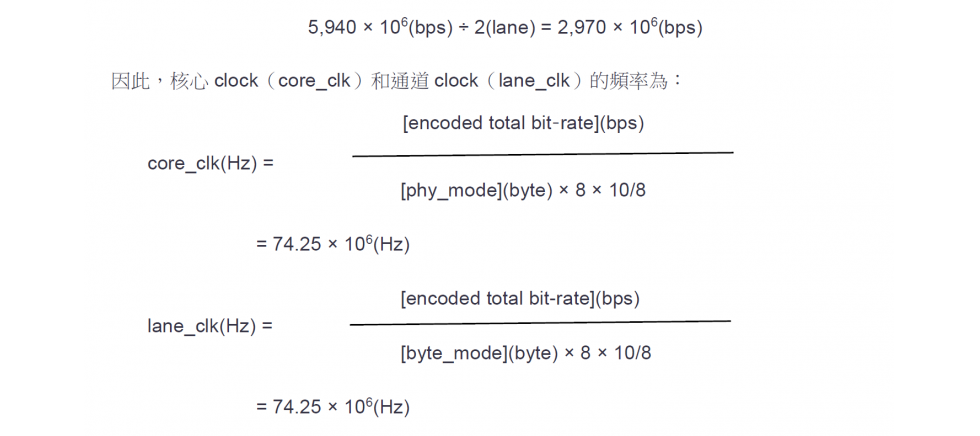

由於VX1的最大傳輸速率為4.0 Gbps /通道,因此系統必須至少具有2條通道,當系統配置為2條通道時,將計算每條通道的傳輸速率:

Example Configuration (RX)

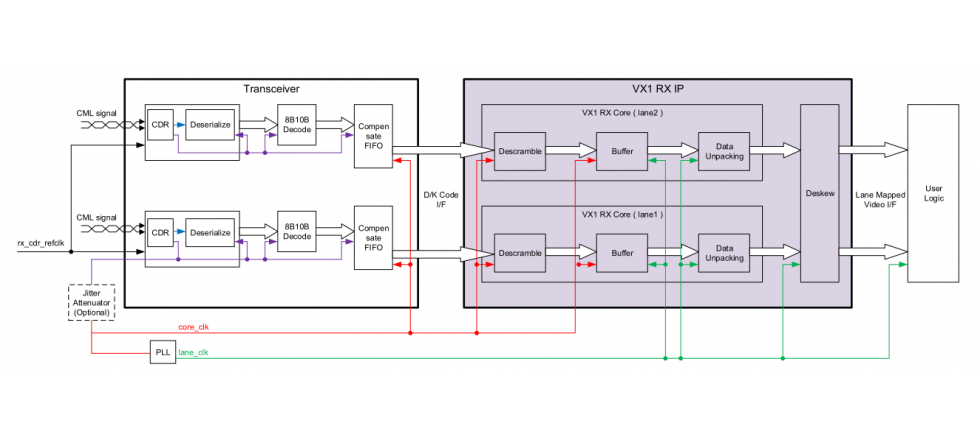

圖3顯示“V-by-One®HS”接收器的示例框圖,其中如果使用兩個通道,則連接 VX1 RX IP,User Logic,PLL和Transceiver。VX1 RX IP需要兩種clock(core_clk 和lane_clk),這些clock必須沒有頻率偏差。lane_clk是由PLL產生,PLL使用Transceiver的CDR clock作為參考clock。因此, User Logic和VX1 RX IP的連接包含lane_clk和Lane Mapped Video Interface

圖3

圖3

Supported Device

Intel FPGA

- Cyclone V GX/GT

- Cyclone 10 GX

- Arria V GX

- Arria 10 GX

- Stratix V GX

- Stratix 10 (H/L-Tile)

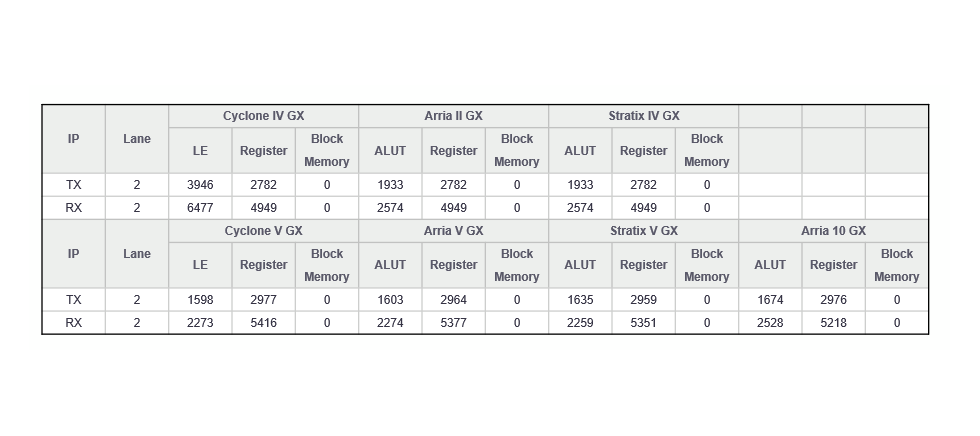

Resource Utilization

圖4

圖4

Macnica Deliverables

- 加密RTL (Verilog HDL)

- 參考設計

- 模擬環境(For ModelSim)

- IP使用手冊

- 參考設計使用手冊

參考文獻

- Mpression, V-by-One® HS Tx IP / V-by-One® HS Rx IP, https://www.m-pression.com/solutions/hardware/v-oner-hs-tx-ip-v-oner-hs-rx-ip,