IP & Software

Macnica offers various types of IP and software for FPGAs and embedded applications with in-depth technical support and design services.

- FPGA IP Cores

- Software

Video/Graphics/Display

Macnica delivers proven IP cores for video, graphics, and display applications, enabling FPGA developers to focus on innovation rather than interface complexity. Our portfolio includes standards-based image sensor, display, and Video-over-IP interfaces, along with a wide range of video and graphics processing functions.

| Image Sensor Interface | SLVS-EC RX | Image sensor interface (Rx side) to Sony CMOS image sensors |

| Display Interface | V by One® HS (Tx/Rx) | High-speed serial interface compliant with V-by-One HS standard by tdine Electronics |

| V by One ® HS Plus (Tx/Rx) | ||

| HDMI 2.0 (Tx/Rx) | High-speed interface compliant with HDMI 2.0 standard | |

| Graphics | Rotating Video Frame Buffer (RVFB) | Rotates video in 90-degree increments |

| Video & Vision Processing (VVP) | A collection of FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs. | |

| Video Analytics Library | Functions for different types of histogram displays plus a video rotate function. | |

| OSD Color Palette | Converts 8bpp Avalon Streaming video from a Frame Reader or other component into a 24- or 32-bpp video stream via a programmable color palette | |

| Broadcast Video over IP Networks | ST 2110 / ST 2022-6 / ST 2059 | Production-proven package of RTL, SDKs, reference designs and documentation to turn Altera® SoC FPGAs into reliable, SMPTE ST 2110/2022/2059 standards-compliant media nodes at 10/25/40/100 GbE. |

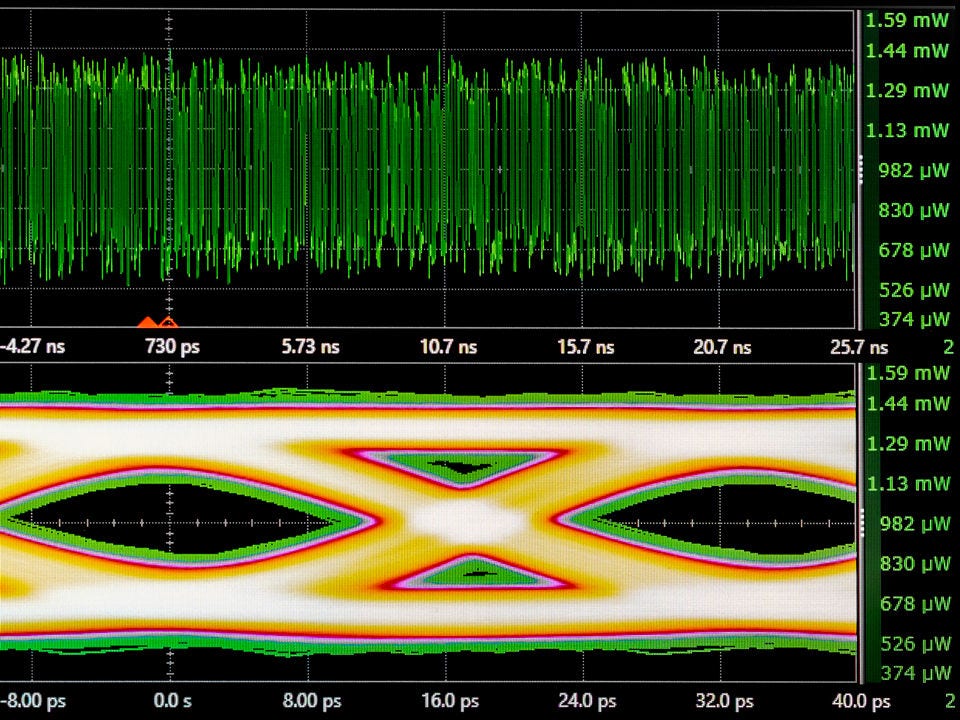

Inter-Chip/Board High-Speed Serial I/O

Macnica’s ION Interface IP Cores deliver ultra-high-speed serial connectivity between chips and boards, engineered for Altera FPGAs with high-speed SerDes. Built on Macnica’s proprietary ION protocol, these IP cores ensure exceptional performance and signal integrity without compromise.

| ION Interface | High-speed serial interface (13.5 Gbps max.) with a lightweight protocol | |

High-speed serial interface (8 Gbps max.) using a lightweight protocol |

Networking

Networking is one of the most powerful applications for FPGA technology. Leveraging deep expertise in network protocols and real-world use cases, Macnica and Design Gateway deliver high-performance, flexible networking solutions in easy-to-use IP core formats.

| MAC | 10G MAC Lite | Simple to use, light version of a 10Gb Ethernet MAC, perfect for chip-chip or backplane communications |

| QUIC protocol | Design Gateway QUIC Client 10Gbps | Fully offloads the CPU from handling TLS 1.3 handshakes, encrypting/decrypting payload data, and managing both QUIC and UDP/IP layers |

| TCP/IP Offloading Engine | Design Gateway TOE (1G - 200G) | Pure hardware TCP/IP protocol stack for Agilex 7 I-Series FPGA |

| UDP Offloading Engine | Design Gateway UDP (1G - 100G) | All hard-wired UDP/IP protocol stack for Agilex 5 FPGA |

| FinTech Networking Package | Design Gateway Low-Latency Fintech IP Series | Package of IP cores optimized for high throughput trading (HST), market data processing and tick-to-trade systems for financial trading |

Storage

In data-intensive applications, high-performance storage access is essential. Design Gateway, in partnership with Macnica, provides advanced storage interface IP cores optimized for Altera FPGAs to deliver maximum throughput and reliability.

| NVMe | Design Gateway NVMe | Standalone NVMe Host Controller with built-in optimized PCIe Bridge and Internal Memory Buffer, designed to handle NVMe Protocol without CPU/OS and External DDR memory. It’s recommended for applications that require high performance, high storage capacity, in very compact systems, and easily supports multiple NVMe SSDs. |

| Design Gateway raNVMe-IP | Random I/O optimized NVMe host in pure logic for very high IOPS without a CPU or external DDR. | |

| Design Gateway muNVMe | Designed and optimized for multiple data stream access to single NVMe SSD by multiple users simultaneously. muNVMe-IP can achieve close to SSD's maximum possible throughput for both mixed read/write and same direction access. This IP is recommended for the application that requires high performance & multiple data streaming or sequential access over single NVMe SSD by pure hardware logic without CPU/OS. Customization to increase the number of users is possible upon customer's requirements. | |

| Design Gateway rmNVMe-IP | Combine random I/O optimization with concurrent multi-user access in a single hardware NVMe host that does not require a CPU or external DDR. | |

| Design Gateway NVMe TCP/IP | Standalone host-side NVMe Over Fabric (NVMe/TCP) controller with no CPU and external memory required. | |

| SATA | Design Gateway SATA | SATA IP core provides link layer to implement SATA channel to Altera FPGAs. It supports SATA-III (6Gbps) and matches with SATA-III SSDs. |

Security

Security is essential in today’s embedded systems, protecting both users and organizations from growing threats. Design Gateway’s Security IP Cores, available through Macnica, help FPGA developers integrate robust protection and accelerate secure system design.

| TSL | Design Gateway TLS1.3-IP | CPU-less and high-performance TLS v1.3 protocol engine for FPGA acceleration with no CPU and external memory required. |

| AES | Design Gateway AES256-GCM-IP | Advanced Encryption Standard (AES) with a 256-bit key in Galois/Counter Mode (GCM), which is widely used for Authenticated Encryption with Associated Data (AEAD) applications. |

| Design Gateway AES256-XTS-IP | Advanced Encryption Standard (AES) with XEX (XOR Encrypt XOR) tweakable block cipher which operates sequences of complete blocks and is widely used in protecting the confidentiality of data on various storage devices with interfaces such as NVMe and SATA. We also have a lineup of "2X" ideal for NVMe PCIe Gen4, and "4X," supporting Gen5. | |

| Design Gateway AES128/256-IP | AES-256SS IP specializes in ultra-high throughput and ultra-low latency. IP computes 128-bit data blocks in every 1 clock cycle. Delivering 128Mbps throughput per 1MHz such as 51.2 Gbps @ 400MHz. AES-128 IP is 1st member of AES (FIPS-197) IP Series, designed to support ECB mode for both encryption and decryption. AES128-IP computes 128-bit data blocks within constant 11 clock cycles. Delivering 11.6Mbps throughput per 1MHz such as 5.8 Gbps @ 500MHz. | |

| SHA | Design Gateway SHA256-IP | SHA-224, SHA-256, SHA-384, SHA-512, SHA-512/224, and SHA-512/256 secure hash algorithms. The core is fully-compliant with the FIPS PUB 180-4 (Federal Information Processing Standard) specification. Suitable for applications such as secure communication, password authentication, and blockchain data integrity. |

| TCAM Engine | Design Gateway tCAM-IP | High-performance, extremely low-latency, and highly configurable ternary content-addressable memory IP. tCAM-IP can make continuous deterministic search at 400 MSPS with constant latency of 7 clock cycles. |

Vision System Interface

Macnica offers a full range of FPGA IP cores designed for industrial vision systems. From high-speed image sensor interfaces to robust output interfaces for industrial cameras, our portfolio ensures reliable performance and easy integration. More options are available - please inquire.

| Image Sensor Interface | SLVS-EC RX | Image sensor interface (Rx side) to Sony CMOS image sensors |

| Machine Vision Camera Interface | CoaXPress® Device IP Package for Altera® FPGAs | High-speed image transmission at 6.25Gbps via coaxial cable |

Software

Macnica offers a wide range of software solutions, from lightweight operating systems for embedded devices to high-performance computing applications for broadcast and surveillance markets.

Tiny RTOS

Multi-task, real-time OS for small embedded devices. High-speed task scheduling is provided with a mall-code footprint, making this operating system perfect for your multitasking needs.

| RTOS | Scorpius™ RTOS for IoT Devices | Multi-task real-time OS for small embedded devices |

Broadcast and ProAV

Our broadcast and ProAV offerings range from FPGA IP cores to software components and hardware solutions that device manufacturers and end users in the field can use.

Video over IP | Macnica’s Media Streaming (M2S) SDK enables software-based SMPTE ST 2110 and AMWA NMOS IS-04/IS-05 streaming on general-purpose servers, supporting both standard and specialized NICs - including the MEP100 SmartNIC. |

Video Security Surveillance

Our broadcast and ProAV offerings range from FPGA IP cores to software components and hardware solutions that device manufacturers and end users in the field can use.

| Security Surveillance | Icetana | AI-driven video analytics surveillance software designed to automatically identify unusual or unexpected events in real-time, allowing security operators to move from reacting to situations to working proactively to prevent them. |