TOE200G-IP, 200G TCP Offload Engine

- Product Image

200G TCP in hardware for multi-stream, line rate transport without a CPU or external DDR.

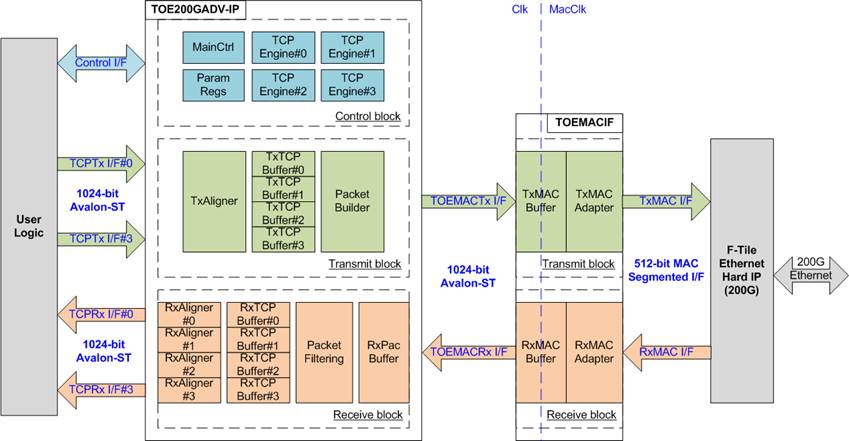

TOE200G-IP implements the full TCP stack in logic and connects directly to 200 GbE MAC and PHY on supported FPGA platforms. The core is built for sustained multi-session throughput with predictable latency and a simple streaming interface to user logic.

Highlights

- Hardware TCP server and client with multi-session scheduling and scalable queues

- AXI4-Stream payload interfaces and register control for configuration and status

- Works with 200 GbE MAC and PCS blocks including RS-FEC where required

- Reference projects for half duplex and full duplex tests, ping reply, parameter setting, and integrated throughput apps

Why Macnica?

- Queue sizing and connection planning for 200G targets, including jumbo MTU recommendations

- Transceiver and RS-FEC configuration on Agilex F-Tile, plus validated MAC selections for 200G links

- Lab validation plans for soak tests and packet integrity at line rate

- Integration with NVMe or NVMe over TCP storage paths for capture and replay

- Supply and evaluation hardware coordination so you can move from demo to pilot without stalls

Key Specifications

- Ethernet: 200 GbE

- User interfaces: AXI4-Stream for Tx and Rx, register interface for control and stats

- Resources: Pure RTL, no external DDR, no embedded CPU in the data path

Typical Applications

- 200G packet brokers, recorders, and telemetry pumps

- Remote capture to storage nodes and NVMe over TCP front ends

- Market data and analytics gateways that require stateful transport

Resources

Get Started

Share target sessions, MTU, and throughput budget. We will size queues, recommend a 200G MAC configuration, and map a demo on your Agilex board.