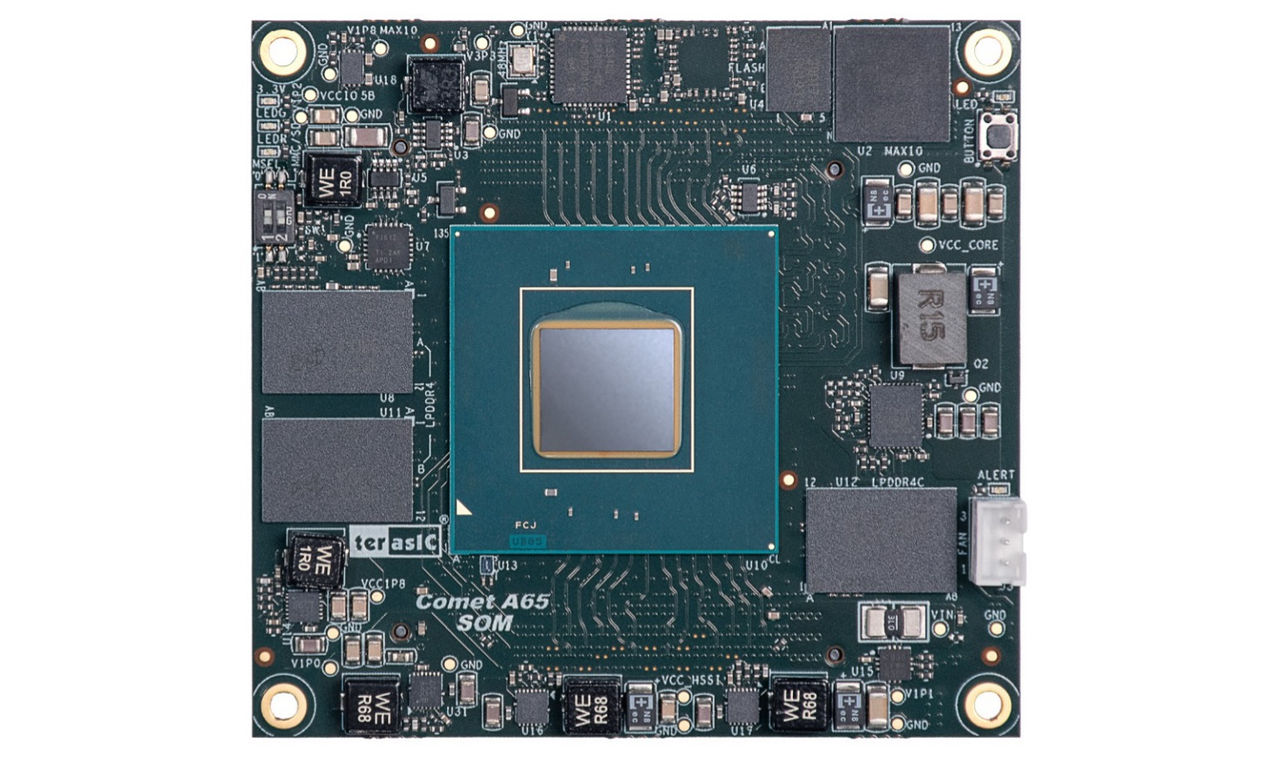

Terasic Comet A65 SOM

Accelerate your Agilex™ 5E SoC based design with Comet A65

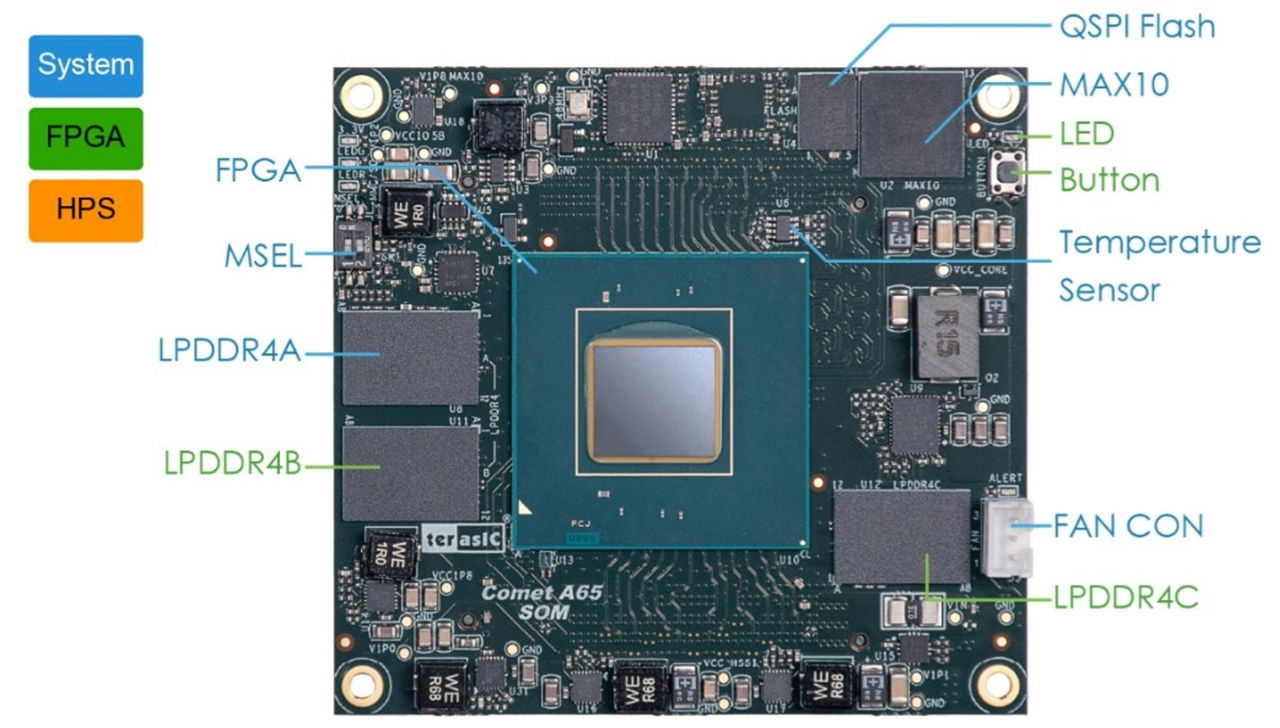

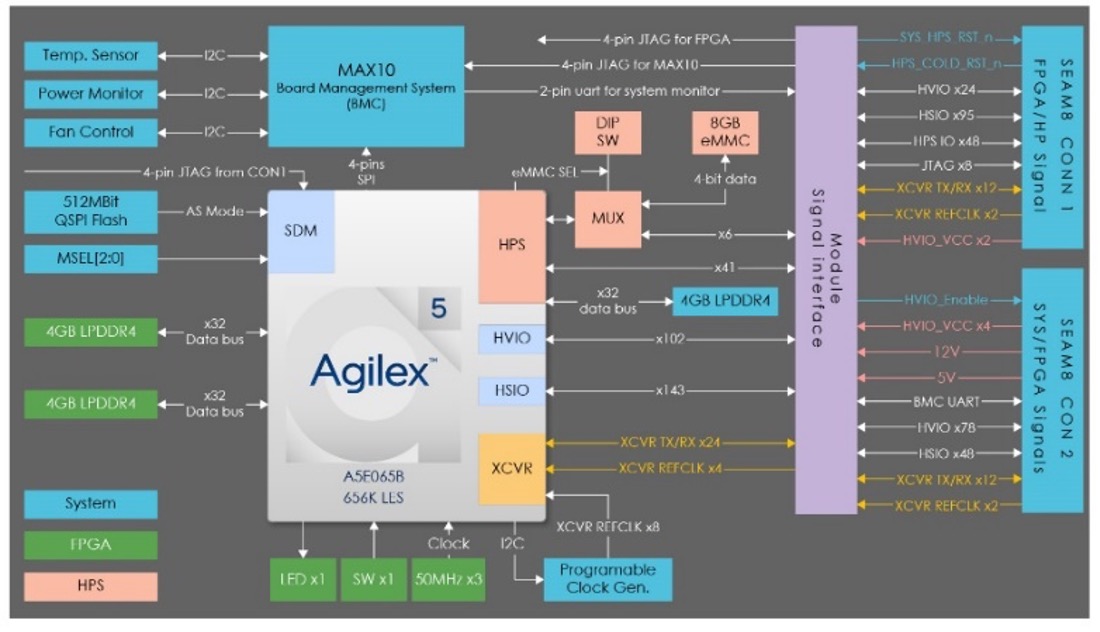

The Terasic Comet A65 SoM’s Agilex5 FPGA integrates dual 64-bit ARM Cortex-A76 cores and dual 64-bit ARM Cortex-A55 cores operating up to 1.4GHz and 1.25GHz, respectively. This heterogenous ARM architecture permits the Cortex-A76 cores to handle the application-level tasks while the Cortex-A55 cores handle the real-time hardware management tasks. The ARM cores (Hard Processor System: HPS) are connected to 4Gbyte of external LPDDR4 memory which can be shared with the FPGA. The HPS peripherals include the three Gigabit Ethernet MACs, timers and USB2.0/USB3.1/eMMC-SD/NAND/DMA/I2C/I3C/UART/SPI controllers which are all available to the user on this SoM.

Two additional external 4GByte 32-bit banks of LPDDR4 memory are connected the FPGA fabric. Other memory devices are the QSPI flash device for FPGA configuration and the standard 8GB eMMC can be increased up to 64GB for HPS boot, OS and application code storage as needed. The SoM’s user programmable FPGA I/O power inputs and FPGA I/Os are connected to the two 500-pin board-to-board connectors which permits a very high number of signals to be available to the user’s carrier board; 102 HVIOs, 143 HSIOs, 48 HPSIOs and 24 17.16Gbps Transceivers.

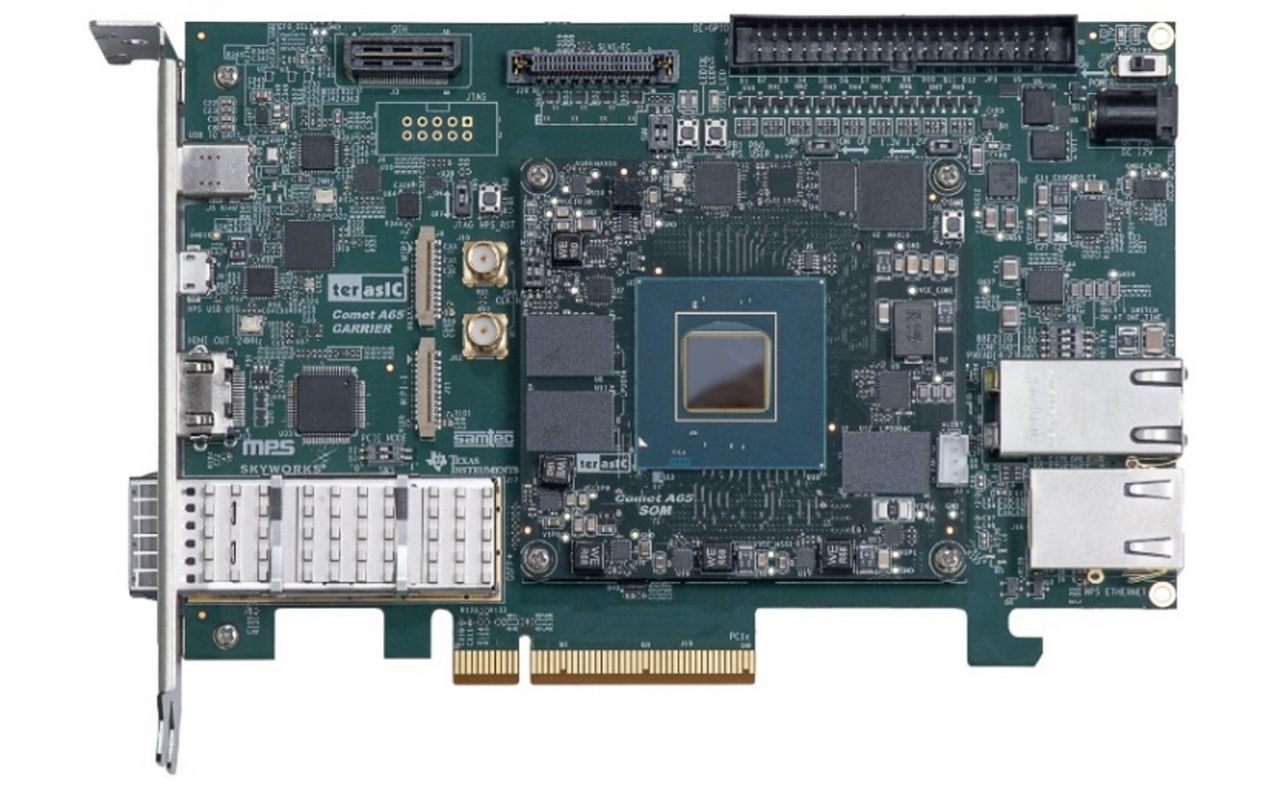

The Comet A65 SoM development kit’s carrier board is a full height, half-length PCIe card with a x8 PCIe edge connector. The on-board USB Blaster III and HPS console UART are both connected to the USB-C connector enabling FPGA design/configuration and ARM software development/debug.

SoM Carrier Board FPGA I/O Interfaces:

- SLVS-EC 3.1 x8

- PCIe Gen4 x4

- HDMI 1.4 output

- QSFP+

- Two 22-pin MIPI x4

- 17 LVDS I/Os

- 40 GPIOs

- Two SMA differential clock inputs

- 2.5G Ethernet

SoM Carrier Board HPS I/O Interfaces:

- MicroSD socket

- Serial UART

- USB 2.0 OTG

- Gigabit Ethernet

System:

- FPGA: A5ED065BB32AE4S (Agilex™ 5 E-Series Device Group B*)

- Module Size : 70mm x 75mm

- 102 HVIO (3.3V x4, 1.8/2.5/3.3 x98)

- 143 HSIO (71 LVDS)

- 48 HPSIO

- 24 Transceivers

- Interface: Two SEAM8 Connectors (8x50 pin)

- Board Management System

- Power and Temperature Monitor

- Auto Fan Control

- Auto shutdown when power or temperature is abnormal

* Compatible with Group

FPGA Side:

- LED x1, KEY x1

- Fixed 50/100MHz Clock

- Programmer Clock Generator for transceiver reference clock

- LPDDR4-A: 4GB DDR4 with 32-bit data bus (no ECC), shared with HPS

- LPDDR4-B: 4GB DDR4 with 32-bit data bus (no ECC)

- LPDDR4-C: 4GB DDR4 with 32-bit data bus (no ECC)

- 102-pin HVIO and 143-pin HSIO connected to SEAM8 connector

- 24 transceiver and 4 reference clock connected to SEAM8 2 connectors

HPS Side:

- LPDDR4-A: 4GB DDR4 with 32-bit data bus (no ECC), shared with FPGA

- 48 HPS IO connected to ADF6 connector

- 8GB eMMC (Expandable) + eMMC SEL Switch